# LOW POWER INTEGRATED SYSTEM FOR A SIMULTANEOUS TIME AND ENERGY MEASUREMENT IN THE PANDAMICRO-STRIP DETECTOR

# Low power integrated system for a simultaneous time and energy measurement in the PANDA micro-strip detector

Inaugural-Dissertation zur Erlangung des Doktorgrades (Dr. rer. nat.) der Justus-Liebig-Universität Gießen im Fachbereich 07 Mathematik und Informatik, Physik, Geographie

**VORGELEGT VON**

Alberto Riccardi

**AUS BIELLA, ITALIEN**

Dekan: Prof. Dr. Bernhard Mühlherr

Prodekan: Prof. Dr. Kai-Thomas Brinkmann

Betreuer und 1. Gutachter: Prof. Dr. Kai-Thomas Brinkmann

2. Gutachter Prof. Dr. Claudia Höhne

### **ABSTRACT**

The  $\overline{P}ANDA$  experiment is one of the main projects foreseen at the Facility for Antiproton and Ion Research (FAIR). Its task is to measure the products of the reactions between an antiproton beam, with a beam momentum between 1.5 GeV/c and 15 GeV/c, and a proton or nucleon fixed target. In order to acquire data on many physics channels at the same time, it is necessary to have a trigger less experiment.

The innermost detector of  $\overline{P}ANDA$  is the Micro Vertex Detector (MVD). The MVD has to distinguish secondary vertexes from the primary one. The detector is composed of two structures, the barrels and the disks, equipped with two types of sensors: silicon hybrid pixels and double-sided silicon micro strips.

The main purpose of this thesis is the design and the first characterisation of PANDA STrip ASIC (PASTA). After a brief overview of the experiment, a complete description of the chip is given. In this part, the motivations that lead to the development of this prototype and the measurement concept are explained. Moreover, the behaviour of all the building blocks, with a particular attention on the analog structures, is shown. In the last part of the thesis the layout, with few details about the implementation of the channels and how the chip was assembled, is described. Finally, after an overview of the experimental setups, the first laboratory analysis of the chip and a preliminary characterisation of a typical channel are reported.

### ZUSAMMENFASSUNG

Das PANDA Experiment ist eines der Hauptprojekte an der im Aufbau befindlichen Beschleunigerzentrum FAIR (Facility for Antiproton and Ion Research). Bei diesem Experiment werden die Reaktionsprodukte, die in Antiproton-Proton- bzw. Antiproton-Kern-Kollisionen mit ruhendem Target entstehen, vermessen. Der hierbei zum Einsatz kommende Antiprotonenstrahl deckt einen Impulsbereich von 1.5 GeV/c bis 15 GeV/c ab.

Um Daten für möglichst viele physikalische Fragestellungen gleichzeitig aufnehmen zu können wird das Experiment mit freilaufendem Trigger durchgeführt.

Der Micro Vertex Detektor (MVD) ist beim PANDA Experiment die strahlnächste Detektorkomponente. Seine Aufgabe ist es unter anderem, die Trennung sekundärer Vertices vom primären Interaktionspunkt zu ermöglichen. Der Detektor besteht aus zwei wesentlichen Teilen, den vier konzentrisch um die Strahlachse angebrachten, zylindrischen 'Barrels' sowie den sechs in Vorwärtsrichtung angebrachten 'Discs' (Scheiben). Hierbei kommen zwei Arten von Sensoren zum Einsatz, Silizium-Hybrid-Pixel und doppelseitige Silizium-Microstrips.

Ziel dieser Arbeit ist das Design und erste Charakterisierungsmessungen des PANDA STrip ASIC (PASTA). Nach einem kurzen Überblick über das PANDA Experiment wird der Chip detailiert beschrieben. Hierbei wird auf die Motivation für die Entwicklung eines eigenen Chip-Prototyps sowie die prinzipiellen Messkonzepte eingegangen. Zudem wird das Verhalten der einzelnen Komponenten, mit besonderem Augenmerk auf den Analogteil, beschrieben.

Im Weiteren wird auf das Layout und die Implementierung der Kanäle sowie die eigentliche Fertigung des Chips eingegangen. Abschließend, nach einer Beschreibung der relevanten experimentellen Aufbauten, werden die ersten Labormessungen sowie eine vorläufige Charakterisierung eines typischen Kanals gezeigt.

# CONTENTS

| 1 | $\overline{P}A$ | NDA EXPERIMENT                                      | 1  |

|---|-----------------|-----------------------------------------------------|----|

|   | 1.1             | Overview of FAIR                                    | 1  |

|   | 1.2             | Physics program of $\overline{P}ANDA$               | 2  |

|   |                 | 1.2.1 Hadron spectroscopy                           | 5  |

|   |                 | 1.2.2 Properties of hadrons in matter               | 9  |

|   |                 | 1.2.3 Nucleon structure                             | 10 |

|   |                 | 1.2.4 Hypernuclei                                   | 11 |

|   | 1.3             | Acceleration structures for protons and antiprotons | 12 |

|   |                 | 1.3.1 The High Energy Storage Ring (HESR)           | 13 |

|   |                 | 1.3.2 Target system                                 | 14 |

|   | 1.4             | $\overline{P}ANDA$ detectors                        | 16 |

|   |                 | 1.4.1 Target Spectrometer                           | 17 |

|   |                 | 1.4.1.1 Tracking system                             | 18 |

|   |                 | 1.4.1.2 Particle identification                     | 21 |

|   |                 | 1.4.1.3 Electromagnetic Calorimeter                 | 23 |

|   |                 | 1.4.1.4 Solenoid magnet                             | 24 |

|   |                 | 1.4.1.5 Muon detector                               | 25 |

|   |                 | 1.4.2 Forward Spectrometer                          | 27 |

|   |                 | 1.4.2.1 Tracking                                    | 28 |

|   |                 | 1.4.2.2 Dipole magnet                               | 28 |

|   |                 | 1.4.2.3 Particle identification                     | 29 |

|   |                 | 1.4.2.4 Shashlyk Calorimeter                        | 30 |

|   |                 | 1.4.2.5 Muon detector                               | 31 |

|   |                 | 1.4.3 Luminosity detector                           | 31 |

|   | 1.5             | Micro Vertex Detector                               | 32 |

|   |                 | 1.5.1 Detector requirements                         | 32 |

|   |                 | 1.5.2 Detector Layout                               | 33 |

|   |                 | 1.5.3 Pixel Detectors                               | 35 |

|   |                 | 1.5.4 Strip Detectors                               | 36 |

| 2 | PAS             | STA ARCHITECTURE                                    | 41 |

|   | 2.1             | Motivation                                          | 41 |

|   | 2 2             | Massurament concent                                 | 12 |

|   | 2.3 | Structure                                  | 45         |

|---|-----|--------------------------------------------|------------|

|   |     | 2.3.1 Channel structure                    | 47         |

|   |     | 2.3.1.1 Front-End chain                    | 47         |

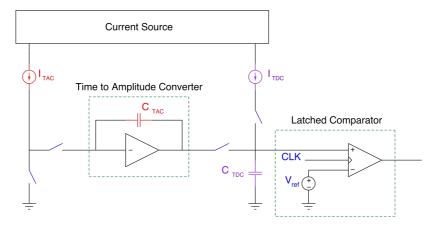

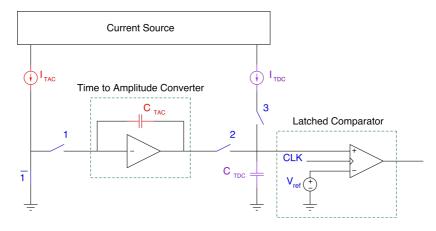

|   |     | 2.3.1.2 Analog TDC                         | 50         |

|   |     | 2.3.1.3 Local Controller                   | 55         |

|   |     | 2.3.2 Global structures                    | 60         |

|   |     | 2.3.2.1 Global Controller                  | 60         |

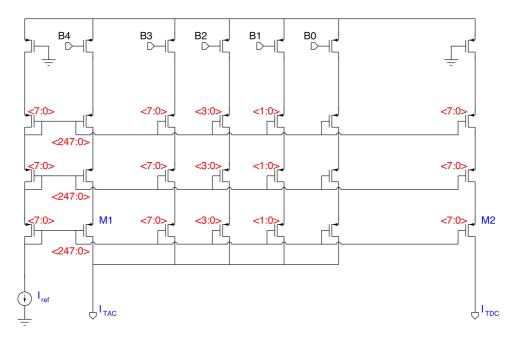

|   |     | 2.3.2.2 Biasing Cells                      | 65         |

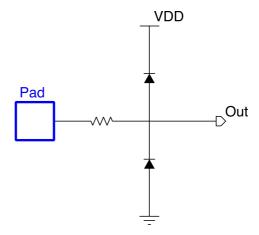

|   |     | 2.3.2.3 Communications points              | 68         |

| 3 | СНІ | PIMPLEMENTATION                            | 73         |

|   | 3.1 | Front-End                                  | 73         |

|   |     | 3.1.1 Preamplifier stage                   | 74         |

|   |     | 3.1.2 Current Buffer                       | 76         |

|   |     | 3.1.3 ToT amplifier stage                  | 77         |

|   |     | 3.1.4 Hysteresis comparator                | <b>7</b> 9 |

|   | 3.2 | Time to Digital Converter                  | 82         |

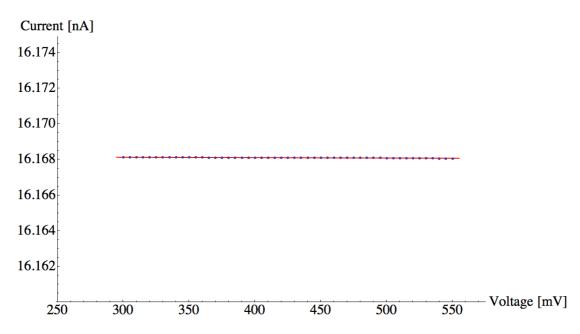

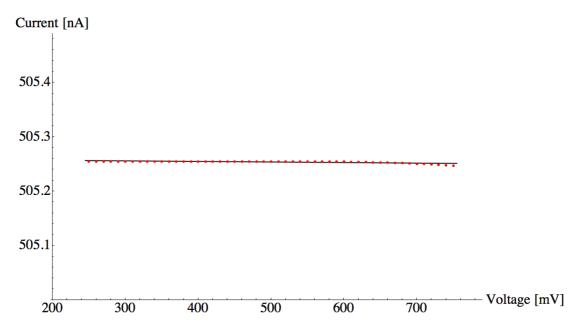

|   |     | 3.2.1 Current generator                    | 82         |

|   |     | 3.2.2 Time to amplitude converter          | 89         |

|   |     | 3.2.3 Latched comparator                   | 95         |

|   | 3.3 | Channel test                               | 98         |

| 4 | PAS | TA LAYOUT                                  | 101        |

|   | 4.1 | General considerations                     | 101        |

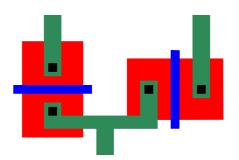

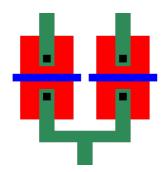

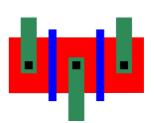

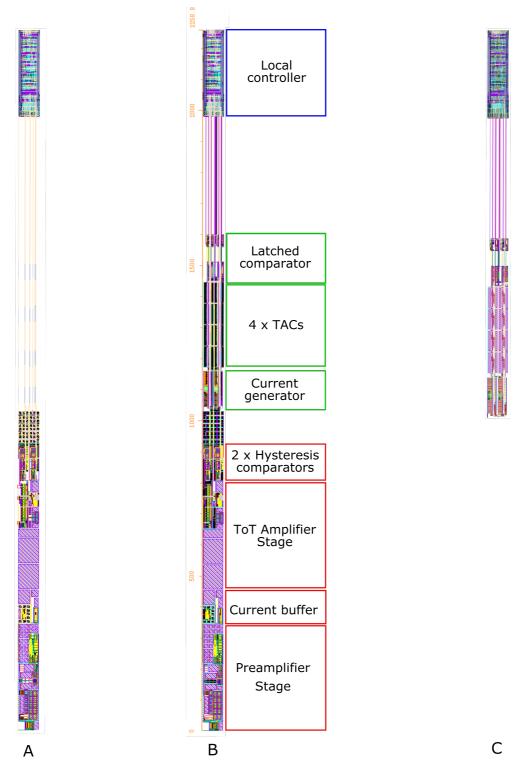

|   | 4.2 | Analog channel layout                      | 106        |

|   | 4.3 | Final assembly                             | 111        |

| 5 | EXP | ERIMENTAL RESULTS                          | 115        |

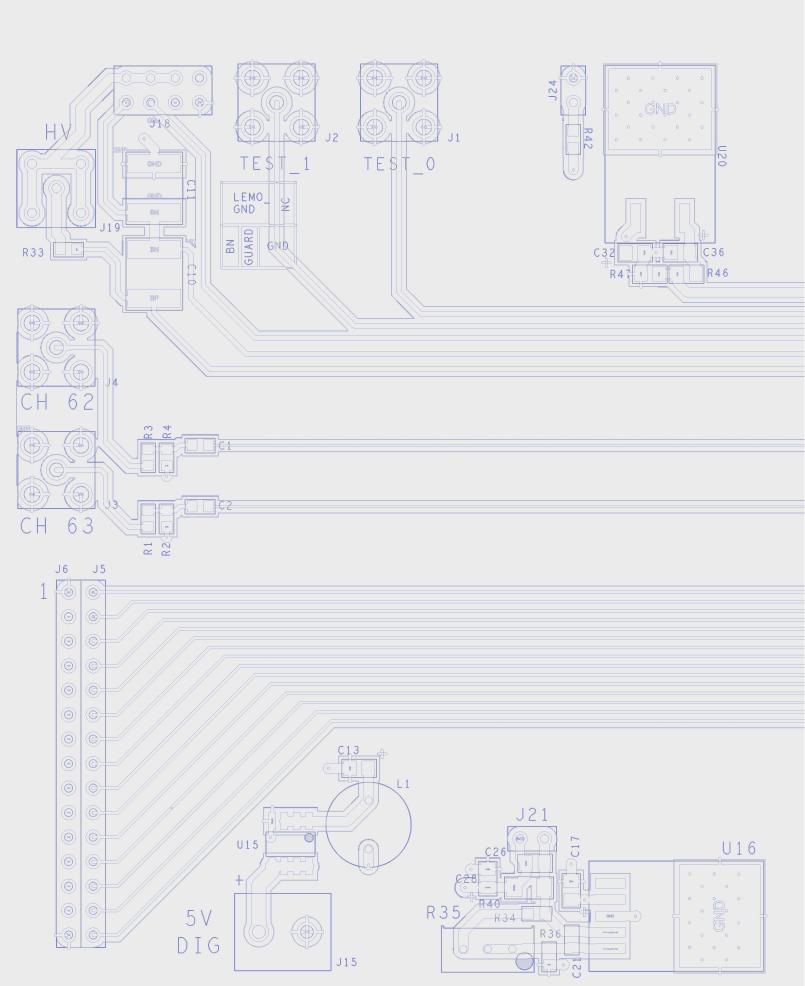

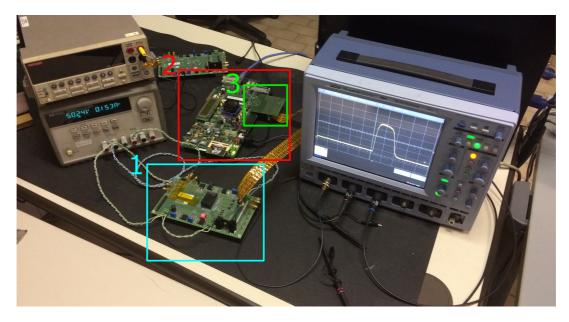

|   | 5.1 | Powering board                             | 115        |

|   | 5.2 | Test board                                 | 117        |

|   | 5.3 | Experimental setups                        | 120        |

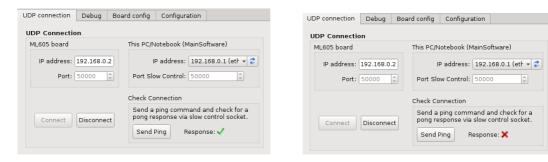

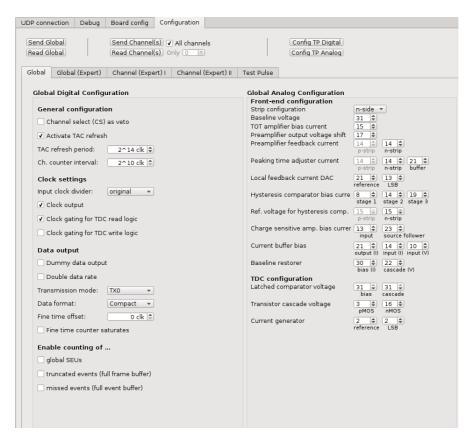

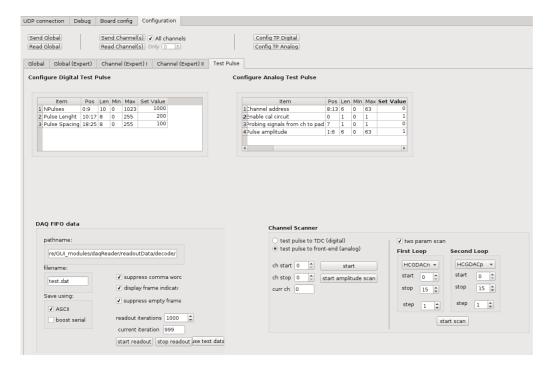

|   |     | 5.3.1 LabVIEW software                     | 120        |

|   |     | 5.3.2 Jülich Digital Readout System (JDRS) | 123        |

|   | 5.4 | Test setup and results                     | 126        |

|   |     | 5.4.1 Configuration of the chip            | 126        |

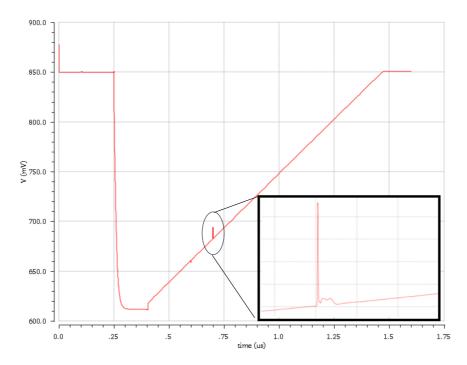

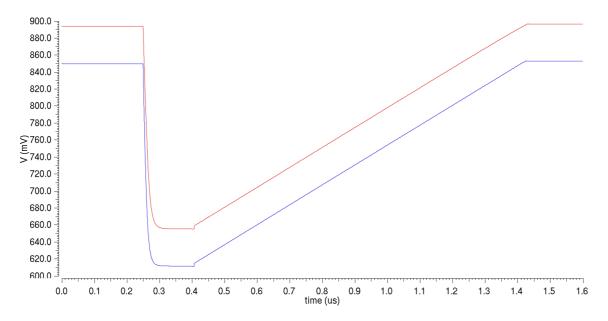

|   |     | 5.4.2 TDC characterisation                 | 128        |

|   |     | 5.4.3 Front End measurements               | 131        |

| 6 | CON | NCLUSIONS                                  | 135        |

| A | PAS | TA USERS GUIDE                             | 139        |

|   | Δ 1 | Description                                | 139        |

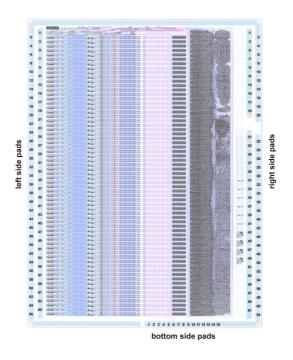

| A.2 PAD Layout             | <br> |  | <br>140 |

|----------------------------|------|--|---------|

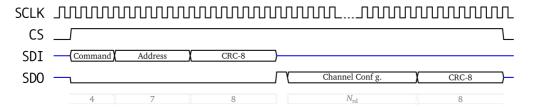

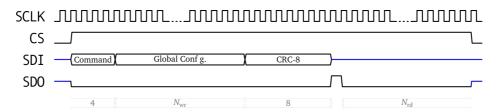

| A.3 Chip Configuration     |      |  | <br>142 |

| A.3.1 Local Configuration  |      |  | <br>144 |

| A.3.2 Global Configuration |      |  | <br>146 |

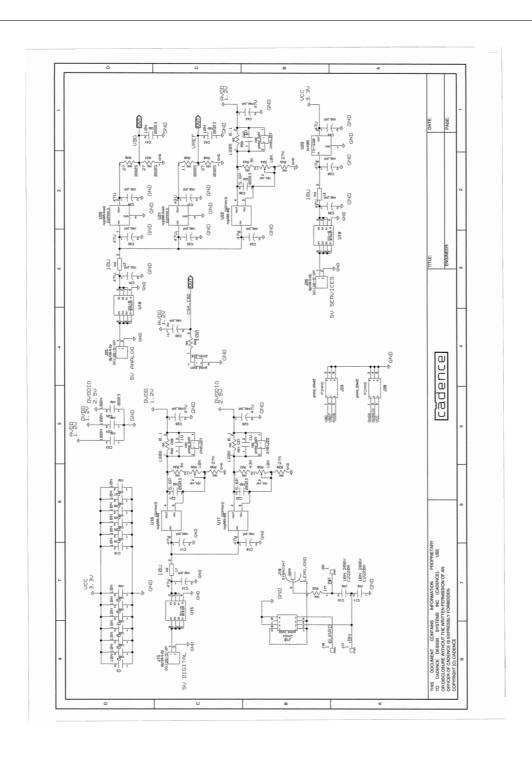

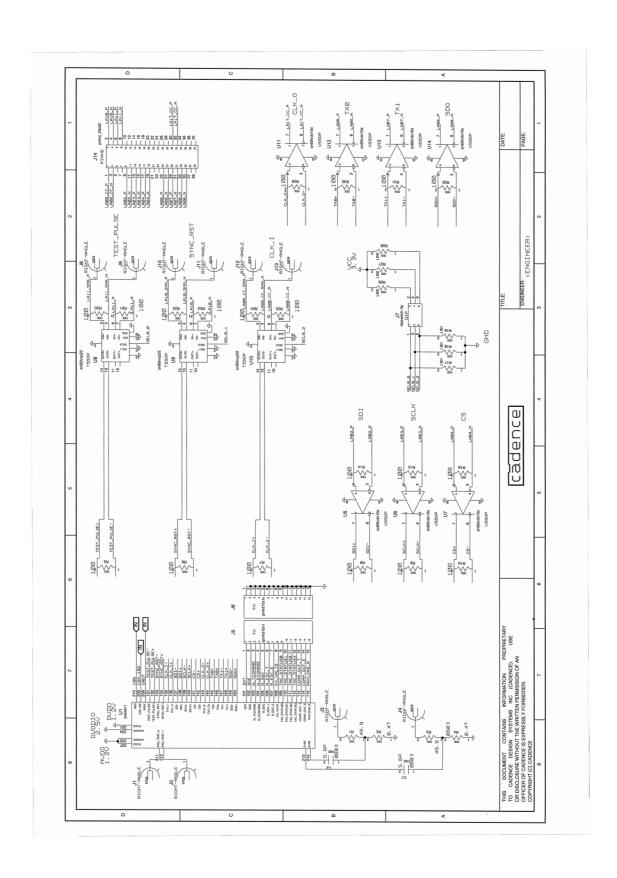

| B DISH SCHEMATICS          |      |  | 149     |

| Bibliography               |      |  | 153     |

| List of Acronyms           |      |  | 159     |

### $\overline{P}ANDA$ experiment

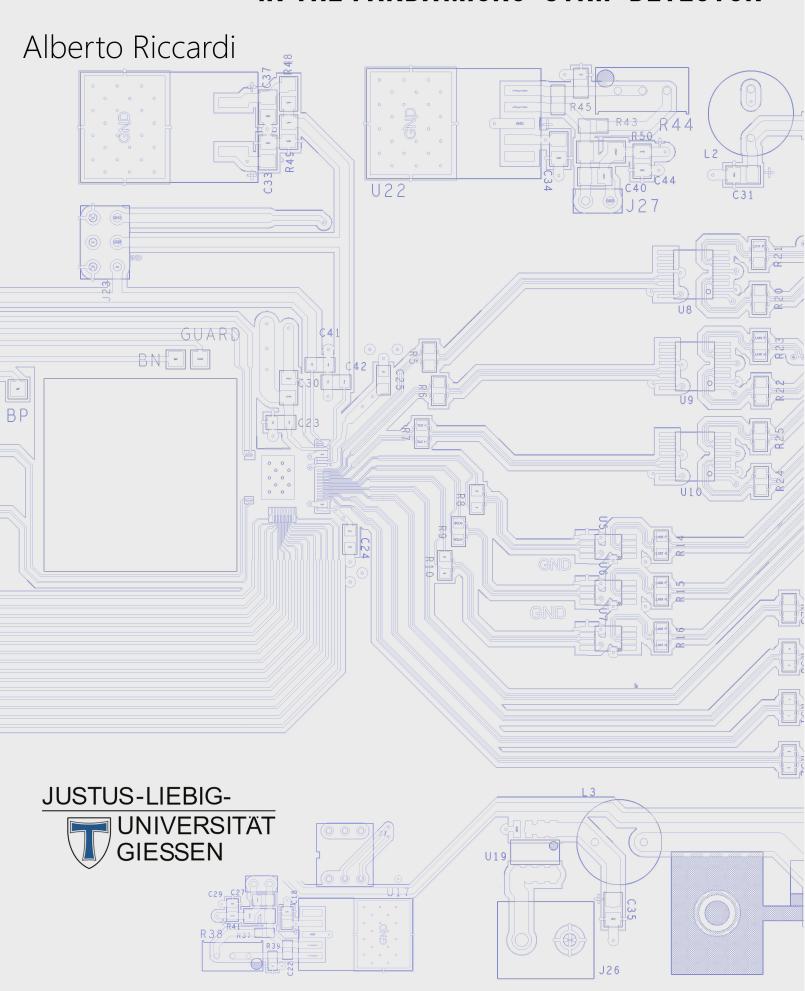

### 1.1 Overview of FAIR

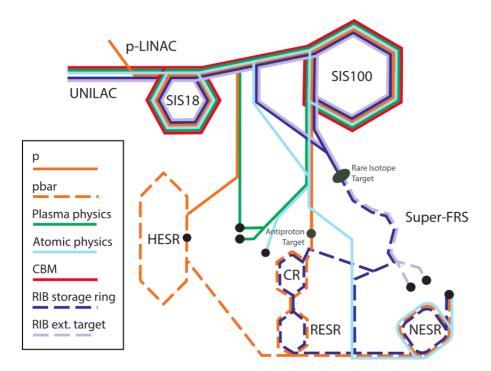

The antiProton ANnihilation at DArmstadt ( $\overline{P}ANDA$ ) experiment is one of the main pillars of the Facility for Antiproton and Ion Research (FAIR) which is under construction in Darmstadt (Germany). The facility, as shown in Figure 1.1, is based on the already existing GSI Helmholtzzentrum für Schwerionenforschung GmbH (GSI) center, which will be the first part of the acceleration chain (blue line). The new structure will have several accelerator rings, the red part of the picture, while in green the four pillars are denoted that group all the different experiments present at FAIR.

Figure 1.1: Overview of the future FAIR facility.

The four pillars are in detail:[1]:

- Atomic, Plasma Physics and Applications (APPA): a set of smaller experiments that investigate plasma physics, ultra-strong electromagnetic fields and radiation effects on materials.

- Nuclear Structure, Astrophysics and Reactions (NuSTAR): like APPA, a collaboration of several experiments, but, in this case, the main task is related to nuclear structure and properties of heavy radioactive elements. Since these elements can be formed in star collapses there is a close connection between this project and astrophysics.

- Compressed Baryonic Matter (CBM): the fields of study are the Quantum ChromoDynamics (QCD) phase diagram in regions of high net baryon densities and moderate temperatures, the deconfinement towards quark-gluon plasma, and matter at neutron starlike densities.

- $\overline{P}ANDA$ : like CBM, a complex detector, in this case the purpose is to study antiproton-proton annihilations in the charm mass regime and antiproton-nuclei interactions. More details about the physics program of  $\overline{P}ANDA$  are presented in Section 1.2.

## 1.2 Physics program of $\overline{P}ANDA$

QCD is a relativistic quantum field theory of quarks and gluons interacting according to the laws of non-abelian forces between colour charges [2] and its Lagrangian density is:

$$\mathcal{L}_{\mathcal{QCD}} = -\frac{1}{4} G_a^{\mu\nu} G_{\mu\nu}^a + \sum_f \overline{q}_f [i\gamma^\mu D_\mu - m_f] q_f \tag{1.1}$$

where f represents the quark flavours, for  $\overline{P}ANDA$  u, d, s, c. The gluon tensor is given by:

$$G_a^{\mu\nu} = \partial^{\mu} A_a^{\nu} - \partial^{\mu} A_a^{\nu} + g f_a^{bc} A_b^{\mu} A_c^{\nu} \tag{1.2}$$

and the gauge covariant derivative involving the gluon field  $A_a^{\mu}$ :

$$D^{\mu} = \partial^{\mu} - i \frac{g}{2} A^{\mu}_{a} \lambda^{a} \tag{1.3}$$

*g* is related to the strong coupling constant as  $\alpha_s(k^2) = \frac{g_s^2(k^2)}{4\pi}$ .

For the high energy regime, a perturbative approach is allowed if the running coupling constant  $\alpha_s$  is smaller than 0.1180 [3].

QCD, as part of the Standard Model, is well understood and tested at high energies [4, 5, 6]. In these conditions, the interaction between quarks and gluons can be described using perturbation theory. However, in the low energy range, QCD becomes a strongly coupled theory and perturbation theory can not be applied. In this regime, many aspects are not yet well understood and a lot of questions are still open. So far, there is not a unique descriptive framework.. The existing framework can be studied with two approaches: the Effective Field Theories (EFT) and the Lattice Quantum ChromoDynamics (LQCD) methods.

### Effective Field Theories

The principle of these theories is to study the strong interaction in a specific regime in a different way, integrating out the degrees of freedom (related for example to high energies) in order to define a scale separation. The Non-Relativistic QCD theory is an example in which heavy quarks are considered to be non-relativistic [7]. Since the gluon dynamics depend on the heavy quark velocity, in the case of  $\overline{P}ANDA$  it depends on the charm quark.

These theories, with hadronic degrees of freedom, have been developed for the description of meson and baryon class properties, since they can provide input to lattice calculations. For the physics program of  $\overline{P}ANDA$  it is possible to use these theories to study hypernuclear dynamics, baryon and open-charm spectroscopy [2].

One more example of EFT, this time based on the partial chiral symmetry of the QCD Lagrangian, is the Chiral Perturbation Theory (ChPT) [8]. This approach can be applied since quark masses are finite, but it is possible to approximate the light quarks, if compared with the hadronic scales, as massless degenerate states. For ChPT there is a spontaneous breaking of the higher chiral symmetry due to hadronic degrees of freedom at low energies. Within the  $\overline{P}ANDA$  physics program, this approach may help the study of possible exotic states in the open-charm sector. Previous studies have already demonstrated that prediction for exotic states can be made, in particular for  $\pi D$  and  $\eta D^*$  channels [9].

### Lattice Quantum Chromo Dynamics

This theory is based on the study of the equations of motion of the QCD Lagrangian, discretising the space-time into a four-dimensional lattice and numerically solving the equations, with a large scale of simulations [10]. For the sake of simplicity, some boundary conditions can be applied and the Z partition function is written as similar as possible to a Feynman's path integral:

$$Z = \int D_{\varphi}(x,\tau)e^{-S_E[(x,\tau)]} \tag{1.4}$$

In equation 1.4,  $\varphi$  is the field in terms of Feynman's integrals,  $D_{\varphi}$  is its differential and  $S_E$  is the Euclidean action. One of the main problems concerns the calculation requirements; for

### 4 $\overline{p}$ and a EXPERIMENT

this reason, several simplifications were adopted. Nowadays, since the computing capability has grown, it is possible to reduce the effects of these simplifications. The mass of some of the open-charm and open-bottom mesons can be calculated by LQCD, as well as the ones of charmonium and bottomonium states [11]. Moreover, studies of the proton form factor, which in  $\overline{P}ANDA$  will be performed analysing the reaction  $\overline{p}p \longrightarrow e^+e^-$ , will also benefit from LQCD.

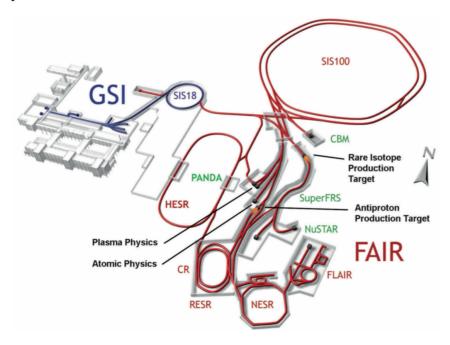

Figure 1.2: Available states as function of invariant mass and antiproton momentum [12].

The  $\overline{P}ANDA$  experimental program comprises several topics related to the strong interaction, in particular, the investigation of QCD. The main goal of  $\overline{P}ANDA$  is to answer some of the open questions in the QCD field, having a program designed to collect high-quality data. Using the High-Energy Storage Ring (HESR), described in Section 1.3.1, it is possible to have an antiproton beam in a high resolution mode. A precision of up to  $\delta p/p = 10^{-5}$  and a resolution of the order of 30 keV [13] allows an accessible mass range from 2.2  $GeV/c^2$  to 5.5  $GeV/c^2$ . The possible states to be studied are shown in Figure 1.2.

The  $\overline{P}ANDA$  physics program can be summarised in four different pillars:

- Hadron spectroscopy

- Properties of hadrons in matter

- Nucleon structure

- Hypernuclei

### 1.2.1 Hadron spectroscopy

The first field of  $\overline{P}ANDA$  is the classification and investigation of the hadronic bound state spectrum, with special attention to mesons that contain charm and baryons containing charm and strange quarks.

### Charmonium spectroscopy

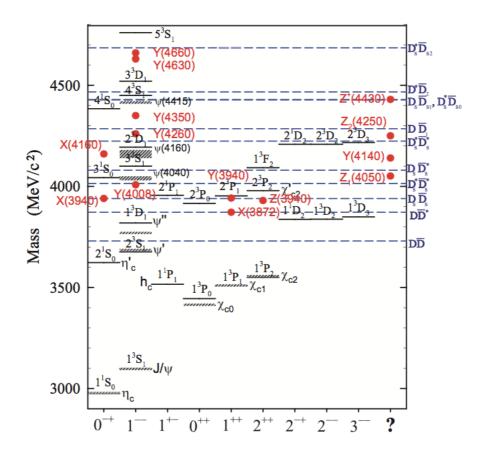

Charmonium, as a  $c\bar{c}$  state, defines a group of neutral meson states. It is considered "hidden charm", since charmonium has a net charm of zero. The first experimental evidence of the charmonium, in particular; the  $J/\psi$  ( $J^P=1^-$ ), was found simultaneously in 1974 by two different groups. The first one is the group of RICHTER, AUGUSTIN, BOYARSKI, et al. at SLAC [14] and, the second is AUBERT, BECKER, et al. [15] at Brookhaven National Laboratory(BNL). Thanks to this discovery, both group leaders got the Nobel Prize in 1976. Even if the state was discovered a long time ago and many experiments were built to study the charmonium spectrum, there are regions of the spectrum that are still not understood. Eight states were discovered, as can be seen in Figure 1.3, in the region below the  $D\bar{D}$  threshold, corresponding to 3.73 GeV. Note that in this region the energy is smaller than the one needed to form a couple of open-charmed ground state mesons. Some of these states have been measured precisely with an error of ten keV for their masses. Other states, like the singlet  $\eta_c$ , have not a precise mass measurement yet. The mass error for the  $\eta_c$  is 1.3 MeV and the one in the total width is 4 MeV [16].

In the Figure 1.3 the solid blacks line correspond to theoretical predictions while the experimental results are shown with shaded lines [18]. The red dots represent states that can be interpreted as charmonium states and consequently the most probable quantum number is shown. There are also states, in the right part of the graph, that don't fit any standard quantum number and for this reason they are called "exotic".

The contribution of  $\overline{P}ANDA$  will not only be the measurement of exotic states with a higher precision but may also increase the resolution of the mass and width for states like the  $\eta_c$ .  $\overline{P}ANDA$  is not the only charmonium oriented experiment, for example at Fermilab there are

Figure 1.3: States of the charmonium spectrum with quantum number assignments [17].

also E760 and E835. However,  $\overline{P}ANDA$  will have a ten times higher luminosity and momentum resolution thanks to HESR and its antiproton beam [2].

### Open charm spectroscopy

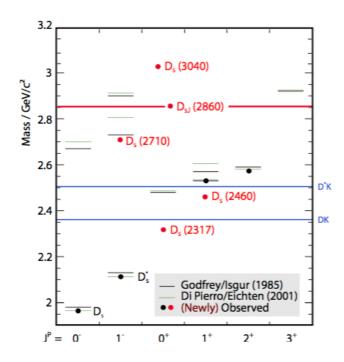

The open charm mesons are composed of one charm and one light quark, giving a non-zero total charm value. The first open charm was detected in 1976; more correctly, there were two different particles, the  $D^0$  discovered by the group of GOLDHABER, PIERRE, ABRAMS, et al. [19] and the  $D^\pm$  by PERUZZI, PICCOLO, FELDMAN, et al. [20]. In the following years many others states have been found, leading to the present spectrum illustrated in Figure 1.4. In the spectrum, the black and red dots represent experimental measurements while the green dotted lines and the black lines come from two different theoretical predictions and the blue lines are the thresholds for decays.

In order to evaluate the two different theoretical interpretations of the spectrum, further experiments are needed and  $\overline{P}ANDA$  could perform relevant studies in this context. One example is the  $D_{s0}^*$  (2317) that has a mass just below the DK threshold and few MeV as the upper limit on

Figure 1.4: Spectrum of open charm meson  $D_s$  [17].

its width.  $\overline{P}ANDA$ , according to the simulations, will have a resolution for the width of these states in the order of 100 keV [21].

### Baryon spectroscopy

Another important feature, in order to have a better comprehension of nonperturbative QCD, is the study of the baryon spectrum [22]. At the moment, this spectrum is not well understood. Indeed, according to the "Review of Particle Physics" [23] for several baryons, important properties like mass width and decay channels are only roughly measured. The agreement between some experimental data and the quark model predictions is also quite poor, since the expected masses are different from the measured ones and some resonances, predicted by the theoretical model, have not been observed yet [24].

$\overline{P}ANDA$  will add important data for the clarification of this spectrum, due to its  $4\pi$  acceptance for particle identification and tracking detectors. This implies that it will be possible to measure the decay of  $\overline{p}p$  into  $\overline{\Omega}\Omega$ ,  $\overline{\Lambda_c}\Lambda_c$  or  $\overline{\Sigma_c}\Sigma_c$  [25]. While at a beam momentum around 3 GeV/c the baryon production probability is similar than the meson one, with the increased momentum (up to 12 GeV/c) the baryon production cross section becomes more and more relevant, with a ratio between baryons and mesons of about two. Indeed, when it will be possible to use the high luminosity mode in HESR, for the  $\Omega$ s, a production of 700  $\Omega$  baryons having a threefold strangeness per hour it is expected [2].

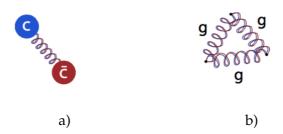

### Gluonic excitation

According to QCD, gluons, as mediator bosons of the strong interaction between quarks, can create bound states. Even if they have not been identified yet, theory predicts two different states: hybrids in which a valence gluon is part of a  $\bar{q}q$  pair (Figure 1.5 a), and glueballs (Figure 1.5 b), that are states composed only of gluons.

Figure 1.5: Model for the gluonic excitation.

### **HYBRID STATES**

In the hybrid system, due to the presence of the gluon that adds another quantum number  $(J^P=1^\pm)$  and another degree of freedom, it is possible to reach energy levels otherwise forbidden to structures that contain only quarks. According to theory, eight states are predicted combining the S-wave mesons with a gluon excitation, three of them having exotic quantum numbers that can not be interpreted as standard  $\bar{q}q$  pairs. Until now the clearest experimental evidence of possible hybrid state comes from the LEAR facility, where  $\bar{p}p$  annihilation were studied. In particular two particles with  $J^{PC}=1^{-+}$  were measured: the  $\pi_1$  (1400) and the  $\pi_1$  (1600) [26]. In the charmonium sector, hybrids are expected to be in the mass region between 3 and 5  $GeV/c^2$ . In the  $\bar{P}ANDA$  experiment, the strategy to find exotic hybrids is to use the highest beam momentum that is possible to reach with the HESR [2].

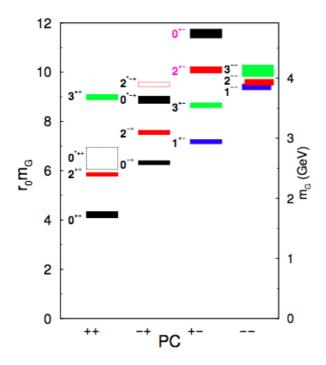

### GLUEBALLS

Fifteen different states are predicted by LQCD calculations in the momentum range provided by the HESR [27] and in  $\overline{P}ANDA$  it would be possible to measure these states. Glueballs with exotic quantum numbers are called oddballs. The lightest oddball predicted by LQCD has a mass of  $4.2\,GeV/c^2$  and  $J^{PC}=2^{+-}$  [28]. In Figure 1.6 the simulated glueball spectrum is reported: the respective quantum number configuration  $J^{PC}$  is the number next to each state. The pink ones are the oddballs states, while the different colours represent their total angular momentum J. The mass is given in two different ways, for the right axis the scale is directly in  $GeV/c^2$  while the scale on the left gives the mass in units of the hadronic scale parameter

$r_0$  as multiples of  $r_0^{-1}$  = 410 MeV [27].  $\overline{P}ANDA$  will have an important role in collecting more statistics compared to the existing measurements concerning regular and light glueballs [29].

Figure 1.6: Spectrum predicted by LQCD for glueballs [30].

### 1.2.2 Properties of hadrons in matter

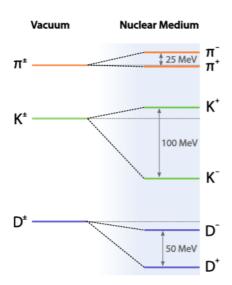

The properties of hadrons change when they are embedded into nuclear matter due to the surrounding interactions. The studies are mainly focused on the modification of the mass level spectrum, as shown in Figure 1.7. Mass values of the hadrons can be modified by the medium in which they have been created. This effect can be attributed to differences in the chiral symmetry breaking due to the finite density value [31].

The in-medium mass shift and splitting have been already studied by several experiments but none of them investigates them using  $\overline{p}p$  annihilations. In  $\overline{P}ANDA$  it will be possible to study low momentum hadrons in a nuclear environment and, since the effects are more pronounced in this energy region, give a comprehensive understanding of this effect. Moreover, with the beam momentum range provided for  $\overline{P}ANDA$  it will be possible to implant charmed mesons in the nuclear matter with high statistics. It is expected theoretically that the mass shift for the  $J/\psi$  is between 5 MeV/c² and 10 MeV/c² while for other states it is much bigger; as in the case of D mesons where the predicted mass shift range is from 50 MeV/c² to 100 MeV/c² [32].

Figure 1.7: Representation of the mass spectrum in vacuum and the nuclear medium [29].

Another interesting field, that is possible to investigate with antiproton-nucleus collisions in the  $\overline{P}ANDA$  environment, is the  $J/\psi N$  dissociation cross section, which needs further studies. The dissociation cross section of  $J/\psi$  and other charmonium states is important for the study of Quark-Gluon Plasma (QGP) in ultrarelativistic nucleon-nucleon collisions [33].

### 1.2.3 Nucleon structure

The nucleons as constituents of matter are an important topic to investigate. In the energy regime of  $\overline{P}ANDA$  it is possible to perform several measurements to study the nucleon structure. One of these studies concerns the Generalized Parton Distributions (GDP) [29, 34] which is usually studied in lepton scattering. Due to the interactions like  $\overline{p}p \longrightarrow \gamma\gamma/\pi^0\gamma$  and using the handbag technique, in  $\overline{P}ANDA$  it will be possible to study even the distribution of partons. Another one is the study of the transverse distribution of the partons within the nucleon. This can be done with Drell-Yan reactions like  $\overline{p}p \longrightarrow l^+l^- + X$ , where  $l^+$  and  $l^-$  represent a lepton pair. In particular, with  $\overline{P}ANDA$  separate studies of the form factors of the proton, magnetic  $|G_M|$  and electric  $|G_E|$ , is feasible in a momentum range up to  $q^2 \simeq 28 \, (GeV/c)^2$  due to the reconstruction of  $\overline{p}p \longrightarrow e^+e^-/\mu^+\mu^-$  [35, 36]. At present only the Fermilab experiments E760 and E835 [37] have provided some data in the region  $q^2 \simeq 15 \, (GeV/c)^2$  but with low statistics, therefore, it is impossible to determine the two coefficients independently in this momentum range [38, 39].

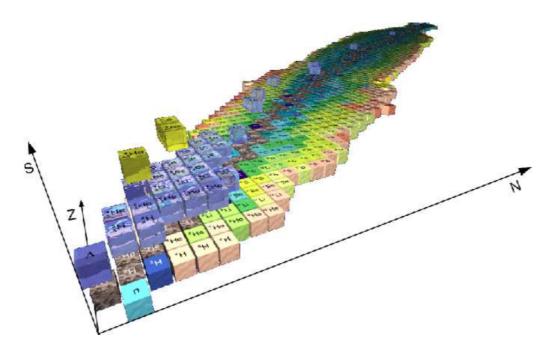

### 1.2.4 Hypernuclei

The last topic of the  $\overline{P}ANDA$  physics program is the study of hypernuclei. Hypernuclei are nuclei where one or two nucleons are replaced with hyperons featuring s quarks. This change implies that the hyperons, bound in the nucleus, have one more degree of freedom. Consequently, the nuclei have the possibility to assume different states that were unaccessible due to previous constraints. The hypernuclei are an interesting tool to study the nuclear structure and energy levels. As represented in Figure 1.8, several hypernuclei have already been found experimentally. In the ground plane (S = 0) nuclei without hyperons are located, the S = 1 plane contains the hypernuclei with  $\Lambda$  or  $\Sigma$  as hyperons while in the plane S = 3 there are nucleons with  $\Lambda\Lambda$  or  $\Xi$  hyperons.

Figure 1.8: Representation of hypernuclei in 3 dimensions, N the number of neutrons, Z of protons and S of strangeness

$\overline{P}ANDA$  will study  $\Lambda\Lambda$  hypernuclei, which are produced in the reaction  $\overline{p}p \longrightarrow \Xi^{-}\overline{\Xi}^{+}$  or  $\overline{p}n \longrightarrow \Xi^{-}\overline{\Xi}^{0}$  [40, 41], using a dedicated experimental setup which modifies the inner part of the  $\overline{P}ANDA$  apparatus. The  $\Xi^{-}$  will be stopped of a secondary target made by sections of silicon detector layers and target foils, where the hypernuclei will be actually formed. Once formed,  $\gamma$ -rays, emitted after the de-excitation of the hypernuclei will be detected by germanium detectors. Approximately 80  $\gamma$ -rays per month are expected [2] since the cross section for  $\overline{p}p \longrightarrow \Xi^{-}\overline{\Xi}^{+}$  is about  $2\mu b$  and the  $\Xi^{-}p \longrightarrow \Lambda\Lambda$  conversion has a probability of around 5% [25].

### 1.3 Acceleration structures for protons and antiprotons

FAIR will be a complex structure with several accelerators, storage and cooler rings in order to fulfil all the requirements from the several experiments at the same time. As seen in Figure 1.9, the consequences of this are several beam lines and different paths depending on the beam itself. The orange line is the path that will be used to obtain antiprotons in the High-Energy Storage Ring (HESR) where  $\overline{P}ANDA$  is situated.

Figure 1.9: Several paths for the beam in the FAIR accelerators and storage rings [42].

The protons will be accelerated up to 70 MeV, by a p-LINAC, with the beam parameters matched to the SIS18. This ring is already used at GSI as a heavy-ion synchrotron but, after the upgrade, it will be possible to store and accelerate also protons to a kinetic energy of 2 GeV in one cycle [42, 43]. The energy reached at this point is enough to be accepted by the SIS100, that has a circumference of about 1,1 km and a magnetic rigidity of 100 Tm. Its goal is to achieve an intensity of  $4 \cdot 10^{13}$  protons per pulse at 29 GeV with a cycle length of 2 seconds. As can be seen in Figure 1.9, after the SIS100, the protons are sent to the antiproton target to generate the corresponding beam. To obtain its maximum intensity the target is the crucial component. Since the antiproton yield grows with the target thickness until the absorption of the produced antiparticles dominates the process. To find the optimum target length two different parameters must be taken into account: the density of the material and its heat capacity. Materials with higher

densities are interesting because they allow having thinner targets, increasing the efficiency of the production. The drawback of these materials is that they have a relatively low heat capacity and this means that the target could melt due to the heat produced by the collisions. After several studies, simulations showed that a 11 cm thick target made of copper or nickel it the best compromise. This means that, with the proton beam coming from the SIS100 at 29 GeV, it is possible to have a production of  $10^{-5}$  antiprotons per primary proton. The resulting antiproton beam of  $10^{8}$  antiprotons is injected into the Collector Ring (CR). This ring is smaller than the previous one, with a circumference of about 211 m and a beam rigidity of 13 Tm. For the whole facility, the CR has three different tasks but only one is related to the antiprotons. Its goals are stochastic pre-cooling of the antiparticles at a fixed kinetic energy of 3 GeV and to bunch the antiprotons in 25 ns bunches.

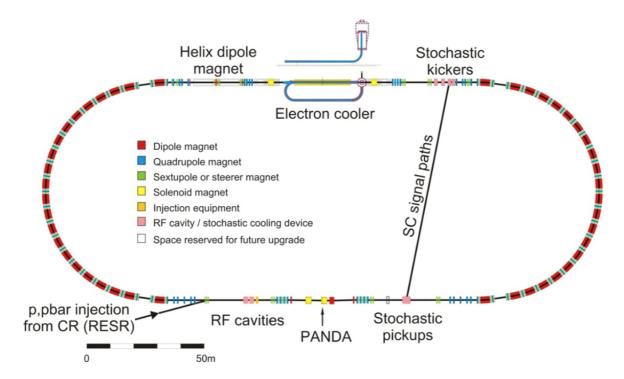

### 1.3.1 The High Energy Storage Ring (HESR)

The HESR is the final ring for the antiproton beam. According to Figure 1.10, the antiprotons are injected from the CR. As written in the previous section, the antiprotons' input energy is 3 GeV. In the HESR, they are accelerated or decelerated to the required energy. The achievable range is from 0.83 GeV to 14.1 GeV, corresponding to a beam momentum of 1.5 GeV/c to 15 GeV/c [44]. With this energy, it is possible to explore the research areas of hadron structure and quark-gluon dynamics. The circumference of the HESR is 574 m, with 132 m of straight sections, and the magnetic rigidity is 50 Tm.

The  $\overline{PANDA}$  experiment will be located in one of the straight sections, while the second one is occupied by the electron cooler. As shown in Figure 1.10, there is also a stochastic cooling present. In particular, the pickup is located close to the end of the experiment straight section while the kicker is at the beginning of the opposite straight section. A stochastic cooling is needed to adjust energy spread and to control the emittance. Since the beam velocity is relativistic, the information necessary to modify the magnetic field by the kicker can not travel faster than the beam. Considering also that the modifications are not instantaneous, it is clear that the path of the data coming from the pickup to the kickers must be significantly shorter than the beam path. This is the reason why pickup and kicker are placed on opposite sides. Using both cooler system it is possible to reach a minimal momentum spread of  $\delta p/p = 10^{-5}$ , but due to the electron cooler the momentum range is limited to 8.9 GeV/c and the luminosity is limited to  $2 \cdot 10^{31}$  cm<sup>-2</sup> s<sup>-1</sup>. This operating mode is called *High-precision mode (HP)*. It is also possible to use just the stochastic cooling leaving out the limitations coming from the electron cooler. In this way it is possible to reach a higher luminosity of  $2 \cdot 10^{32}$  cm<sup>-2</sup> s<sup>-1</sup>, and the full momentum range can be covered. The disadvantage is reflected in a larger momentum spread  $\delta p/p = 10^{-4}$ . This mode is called *High-luminosity mode* (HL).

Figure 1.10: Scheme of the HESR used to accelerate and store antiprotons [45].

### 1.3.2 Target system

The  $\overline{P}ANDA$  physics program, described in Section 1.2, is mainly focused on proton-antiproton interactions. This implies, since the beam is composed of antiprotons, that a pure proton target is needed. It is also planned to study in-medium modifications, thus the target system must be able to provide several materials. For the antiproton-proton interactions, the material chosen is hydrogen, for the antiproton-neutron interactions, the target system is made of noble gases from He to Kr and other gases like  $N_2$ . The most difficult challenge is to introduce the material into the beam pipe without destroying the ultra high vacuum or modifying the beam quality[46]. There are two concurrent projects that fulfil the requirements, a cluster jet or a pellet system. Both will provide a flow of particles with a size in the region of micrometers or nanometers that will cross the beam pipe in the transverse direction.

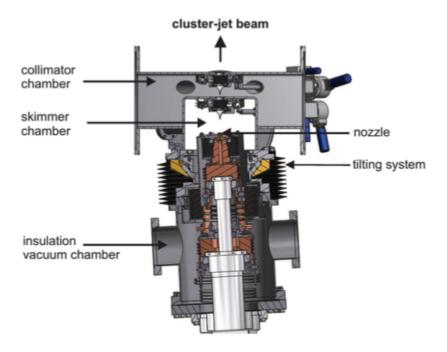

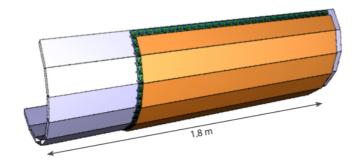

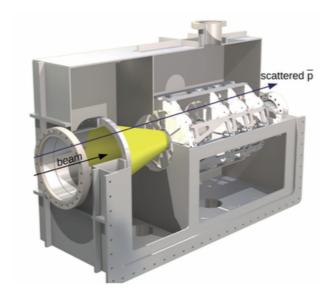

### Cluster target

This target system, shown in Figure 1.11, is based on a pre-cooled gas that is expanded into a vacuum through a convergent-divergent Laval-type nozzle with an opening that can vary from  $10\mu m$  to  $100\mu m$  [46]. In the nozzle, the gas is adiabatically cooled and a supersonic stream is

produced. The resulting gas can travel for several meters in the vacuum without divergence. The cluster features are strongly dependent on the general system design, for example, the size of the cluster and the beam intensity depend on the design of the nozzle (a typical value is  $10^3$ - $10^5$  atoms per cluster) while the final volume density is related to the pressure that the gas has before.

Figure 1.11: Design for the jet cluster target system developed for  $\bar{P}ANDA$  [46].

Once created, the cluster beam passes the skimmer and the collimator chambers to modify its shape. After this, it enters the vacuum pipe leading to the interaction point. In the case of hydrogen fluid, operating conditions are a temperature of 25K-35K and a pressure of up to 25bar.

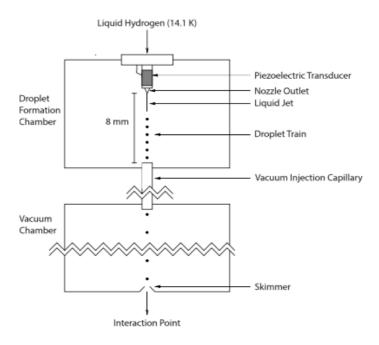

### Pellet target

The pellet target system will be implemented in  $\overline{P}ANDA$  at a later stage. Some of the main advantages are the possibility of an exact target tracking within the beam pipe and the high effective target thickness. However, since the target has a high thickness it is more affected by variations.

As shown in Figure 1.12, to create the pellet first of all a triple point chamber is needed. Here, through a small nozzle, a desired material is injected as a liquid at cryogenic temperatures. The chamber contains the same material injected with the nozzle or in some cases helium in gaseous

Figure 1.12: Schematic for the pellet target system developed for  $\overline{P}ANDA$  [46].

form. The nozzle is periodically stimulated by a piezoelectric trasconducer inducing the jet to oscillate. If the amplitude of the oscillation is equal to the jet radius, the drops are created and thus it is possible to create a continuous and homogenous flow. The latter is injected into the vacuum pipe through a capillary and can be tracked by an optical detector. At this point it is ready to be sent to the interaction point [46].

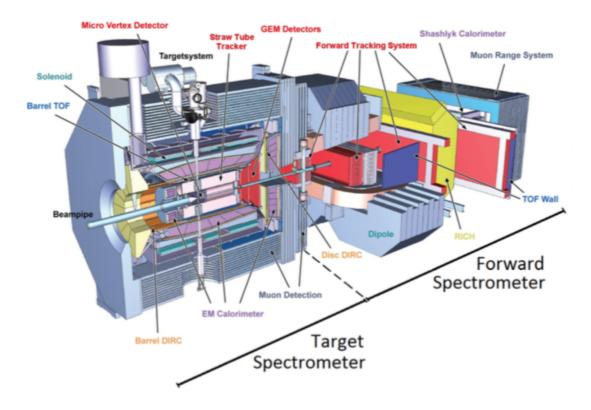

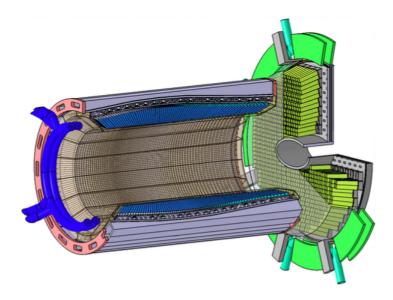

### 1.4 $\overline{P}ANDA$ detectors

Considering the physics program described in Section 1.2 it is clear that a completely custom design for the detector is needed. Since the  $\overline{P}ANDA$  apparatus is an experiment with a fixed target, reaction products will have a boost in forward direction. The detector can be mainly divided into two parts, the Target Spectrometer (TS), that surrounds the interaction point, and the Forward Spectrometer (FS), that extends behind the interaction point, as shown in Figure 1.13. Another important thing to keep in mind during the design of the detectors is the necessity to have, for a high energy and spatial resolution, a  $4\pi$  coverage of the solid angle and a high radiation tolerance against photons, neutrons, kaons and many other particles [46, 29].

Figure 1.13: Overview of the whole  $\overline{P}ANDA$  experiment.

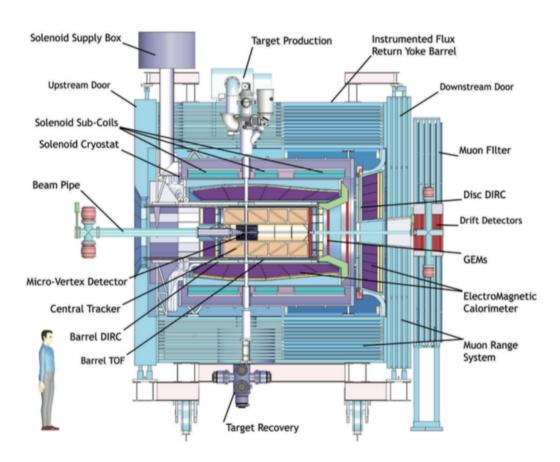

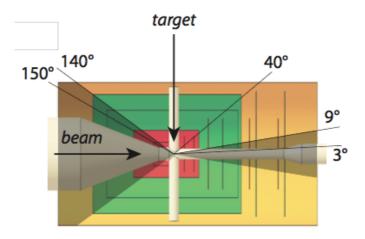

### 1.4.1 Target Spectrometer

The TS, as already mentioned, is placed around the interaction point and consists of several detectors as shown in Figure 1.14. It covers polar angles from 5° (in the horizontal plane) and 10° (in the vertical plane) to 170°. As can be seen in Figure 1.14, the target pipe crosses every layer, from the external magnet to the innermost detector (the Micro Vertex Detector (MVD)). This fact poses one of the most influent constraints for the mechanical design. It is possible to group the structure of the TS in different parts:

- Tracking system

- Particle Identification detectors

- Electromagnetic Calorimeter

- Solenoid Magnet

- Muon Detector

Figure 1.14: Layout of the Target Spectrometer.

### 1.4.1.1 Tracking system

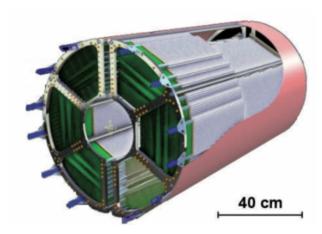

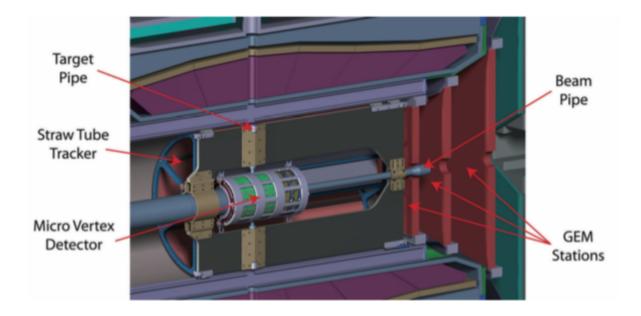

The tracking system is the innermost one and it is made of three different detectors: the Micro Vertex Detector (MVD), the Straw Tube Tracker (STT) and the Gas Electron Multiplier (GEM). In particular, the MVD surrounds the interaction region which in turn is surrounded by the STT. In the forward direction three GEM disks are placed. An overview of the tracking system is shown in Figure 1.17.

### The Micro Vertex Detector

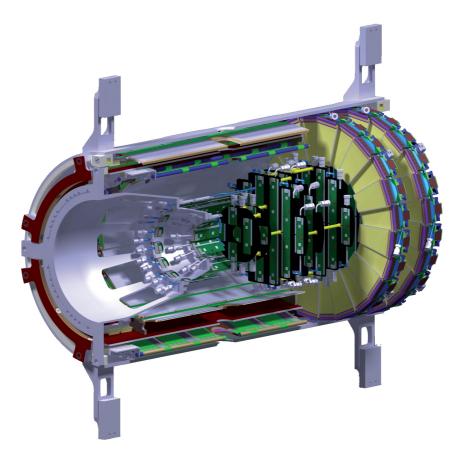

As already mentioned, the MVD is the innermost detector of  $\overline{P}ANDA$ . Its structure, shown in Figure 1.15, is designed to optimise tracking information as close as possible to the interaction region [45].

The main goals of this detector are the primary and secondary vertex reconstruction. This implies that a high spatial resolution, a good radiation hardness and the capability to handle high rates are important features. The material budget must not exceed 10% of one radiation length

Figure 1.15: Layout of the MVD [47].

for the entire acceptance of the detector. Since this thesis is concerned with the development of part of this detector, it will be described in detail in Section 1.5.

### The Straw Tube Tracker

The STT consists of long narrow tubes called straws and it is considered the central tracker of the experiment [48]. The detector in Figure 1.16 has a cylindrical shape, is composed of 4636 straws arranged in 27 layers. Each straw is filled with a gas mixture of Ar and CO<sub>2</sub>with a ratio 90:10 and an overpressure of 1 bar, contained within Mylar aluminised foil with a thickness of  $27 \, \mu m$ . Its diameter is 10 mm while the length is 150 cm. A voltage difference of few kV is generated by the wall of the straws, acting has a cathode, and a single  $20 \, \mu m$  gold plated tungsten wire along the axis of the straw as an anode. This voltage difference produces a drift of both ions and electrons with a maximum drift time of 200ns.

To increase the detector resolution, the 27 layers divided into three different groups. The first one consists of 19 layers that are parallel to the z-axis, this results in a spatial resolution of 150  $\mu m$  in the x-y plane. The second group includes 4 layers that have an orientation of +2.9° with

Figure 1.16: Layout of the STT.

respect to the previous group, while the third one has 4 layers with an orientation of  $-2.9^{\circ}$ . The idea is to alternate 2 layers of the second group with 2 layers of the third group in the middle of the 19 layers. With this structure, it is possible to achieve a resolution of 3 mm in the z direction. The complete design is expected to have a 2.5m longer detector that covers a polar angle between  $10^{\circ}$  to  $140^{\circ}$  with a low material budget in the order of 1.2% of one radiation length.

### The GEM

Particles with small angles are not detected by the STT or they hit this detector in only few points, making the track reconstruction difficult. For this reason, three GEMs will be installed after the STT (Figure 1.17), placed at 1.1m, 1.4m and 1.9m from the interaction point respectively. The diameter increases with the distance, 45 cm for the first disk, 56 cm for the second and 74 cm for the last one. In the center there is a hole for the beam pipe, the latter has a diameter of 5 cm which defines the lower limit of their angular acceptance. With these geometrical limits, it is possible to cover an angular range of 3° to 22°[29, 49].

The three disks act as amplification stages, each GEM is made of a Kapton foil with a thickness of  $50 \, \mu m$  that is micro-perforated. The foils are coated on both sides with copper and applying a high voltage between the two faces it is possible to generate an electric field of around 50 kV/cm. The field lines go into the perforation, increasing the density of the field leading to an avalanche multiplication of the drifting electrons.

Figure 1.17: Layout of the GEM.

### 1.4.1.2 Particle identification

The particle identification is performed using two different approaches, one use the Cherenkov effect while the other using Time of Flight (ToF). For the Cherenkov method two different DIRC detectors (Detection of Internally Reflected Cherenkov light) are planned, the barrel DIRC and the disk DIRC. For ToF measurements, a Scintillator Tile (SciTil) detector is used.

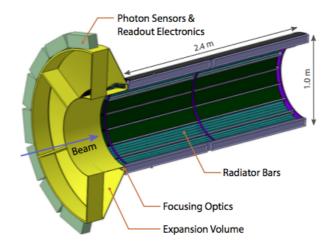

### The Barrel DIRC

The use the Cherenkov method to identify the particles, it is necessary to measure the light emitted from particles that cross a medium faster than the speed of light in that medium. The light is emitted in a cone with a characterising angle  $\Theta_c$  that depends on the particle's velocity  $\beta = \frac{v}{c}$ . Combining this information with the momentum from the tracking system it is possible to determine the mass of the particle.

The barrel part employs the concept developed for the BaBar DIRC [51]. It will cover the polar angle in a range from 22° to 140° [52]. The structure is shown in Figure 1.18 and consists of 80 fused artificial quartz slabs that surround the beam line in a distance of 47.6 cm. At the downstream edge mirrors are placed to reflect the light to the opposite side. At this point the readout is performed. The slabs are coupled to an expansion volume, the light is thus focused on Micro-channel plate photomultiplier tubes (MCP-PMTs), placed in the backside of the volume to convert the light into an electrical signal. The time is measured with a precision

Figure 1.18: Layout of the Barrel DIRC detector [50].

of 100 ps while the angular resolution is around 9 mrad. This structure will be able to provide  $\pi - K$  separation for particle momenta up to 3.5 GeV/c from about 1 GeV/c.

### The Disk DIRC

It is necessary to add the structure shown in Figure 1.19 to increase the acceptance of the DIRC. With this structure, placed at the end of the barrel, it is possible to cover the angular range from  $5^{\circ}$  (in the vertical plane) and  $10^{\circ}$  (in the horizontal plane) to  $22^{\circ}$ . Moreover, is also increases the  $\pi-K$  separation power, in particular, it provides separation up to 4~GeV/c. The disk DIRC has a dodecagon shape with a radius of 110 cm and a thickness of 2 cm. The material is the silica already present in the barrel. The signals are read out with MCP-PMTs or Silicon Photomultipliers (SiPMs) placed on the outer edge of the detector.

Figure 1.19: Layout of the Disc DIRC detector [50].

### The Scintillating Tiles

The SciTil is the ToF detector in the TS, its barrel shape will surround the DIRC detectors. This detector has two different tasks, the first one is to provide a fast response for identification of particles with momenta lower than 1 GeV/c: the output signal has a time resolution of 100 ps [53]. The second task is to provide track seeds for pattern recognition.

Figure 1.20: Layout of the Scintillating Tiles detector [54].

The layout of the detector is shown in Figure 1.20 and includes 8000 plastic scintillator tiles. Each tile has a side that can vary from 20mm to 30mm while the thickness is fixed to 5mm, together they form a barrel. The tiles are read out by two SiPMs each, reaching the time resolution required.

### 1.4.1.3 Electromagnetic Calorimeter

The outermost particle detector in the TS is the ElectroMagnetic Calorimeter (EMC), its layout is shown in Figure 1.21. Its task is to determine the energy of the particles that, crossing the material of this detector, create an electromagnetic shower [55, 56]. The EMC is designed to cover 99% of the  $4\pi$  polar angle. The high count rate and the need for a compact layout leads to different challenges during its design. The maximum energy resolution that is possible to achieve is in the order of 2% while the time resolution is better than 2 ns at 1GeV.

The EMC is divided into three sections, the forward endcap for particles with polar angles between  $5^{\circ}$  and  $22^{\circ}$ , the barrel that is shown in blue in Figure 1.21 for tracks over  $22^{\circ}$  and the backwards endcap, shown in green in Figure 1.21 for particles with polar angles larger than  $140^{\circ}$ . The chosen scintillation material for the calorimeter is lead tungstate ( $PbWO_4$ ), because it has a short radiation length in the order of 8 mm, a fast response and a good radiation hardness. The crystals are 20 cm long and they will operate at  $-25^{\circ}$  C to increase the light yield by a factor of 4 with respect to room temperature. In total 11360 crystals are present in the barrel section along with 3600 in the forward and 592 in the backward end caps. The readout is performed with large area avalanche photodiodes for the barrel and the backward endcap while for the forward endcap a vacuum photo-triode readout system is used [57].

Figure 1.21: Layout of the Electromagnetic Calorimeter [56].

# 1.4.1.4 Solenoid magnet

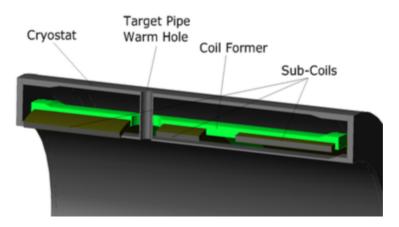

The magnetic field in an experiment like  $\overline{P}ANDA$  is important for particle identification because, measuring the curvature of the trajectory of charged particles and knowing the magnetic field, it is possible to obtain further information about the primary particles. For this task in a solenoid magnet is installed in the TS, which is shown in Figure 1.22.

Figure 1.22: Layout of the Solenoid magnet [58].

The solenoid will provide a homogeneous magnetic field of 2 T, with a maximum fluctuation of 2% [58]. The target system has to pass through the magnet, so a gap has to be left open, as can

be seen in Figure 1.22, which leads to a non-homogeneity of the magnetic field. To avoid this problem, the magnet consists of three coils connected in series, where the outer two have 232 turns while the central one has 104 turns. All three have been designed to work with 5kA. An overview of a section of the magnet is shown in Figure 1.23. For the semiconducting part NbTi is used, specifically, Rutherford-type cables are formed [58]. This means that several cables are grouped together and compressed until a rectangular shape is reached. This technique is important to increase the radial alignment. The wires are then folded inside the coil former that in this case is made of aluminium. There are two different way to increase the strength of the magnetic field in the tracking region: the first one is to build a bigger solenoid, the second and more practical one is to cover the entire magnet with a flux-return yoke made of iron. With this technique it is also possible to achieve a better orientation of the field flux lines and reduce the radial components.

Figure 1.23: Section view of the Solenoid magnet [58].

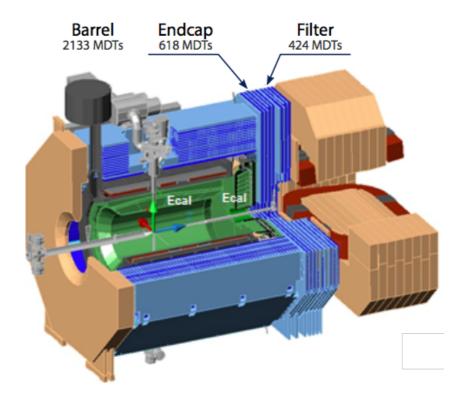

#### 1.4.1.5 Muon detector

Only few particles reach the region after the calorimeter and the solenoid magnet only a few particles are still alive, most of them are pions or high energetic muons. For the Drell-Yan processes, D-meson decays and the  $J/\Psi$  decay, the detection of muons and above all the separation between muons and pions is important.

The structure chosen for the detection of the muons is a Range System, in particular, a series of rectangular aluminium Mini Drift Tubes (MDTs) interleaved in the iron layers of the solenoidal magnet yoke is used [60]. Since the MDTs work as normal drift tubes, it is necessary to add capacitively coupled strips to the rectangular tubes to have the longitudinal position information. With this technique, it is possible to achieve a position accuracy in the order of 1 cm. The muon detector can be split in two parts a barrel and a forward endcap. The first one consists

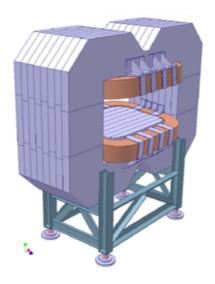

Figure 1.24: Layout of the muon detector with the respective MDTs [59].

of 13 MDT layers interspersed with iron foils. Every iron section has a thickness of 3 cm except for the first and last that have a thickness of 6 cm. The second part is composed of 6 layers of sensitive material, each one is separated from the other by an iron foil for a total of 5 iron layers. In this part, each section is 6 cm thick and it is designed for higher particle momenta. As shown in Figure 1.24 behind the endcap a muon filter made of 5 MDTs! layers and 4 iron layers is placed, to increase the detection capability but also to shield the forward magnet to the solenoid.

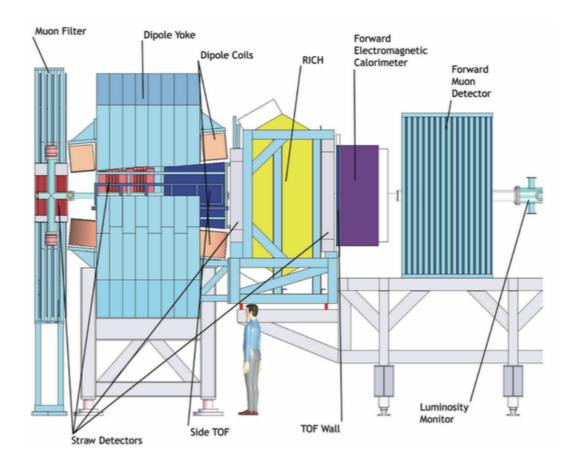

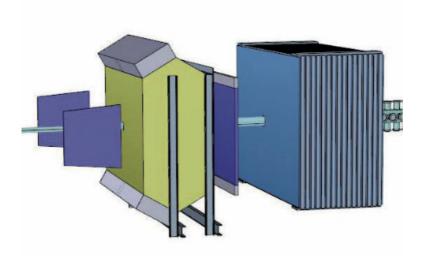

# 1.4.2 Forward Spectrometer

The FS covers the angular range below the  $5^{\circ}$  in the vertical plane and  $10^{\circ}$  in the horizontal direction. It is placed behind the TS as shown in the left part of Figure 1.25. The structure of the FS is grouped in different parts:

- Tracking system

- Dipole Magnet

- Particle Identification detectors

- Shashlyk Calorimeter

- Muon Detector

Figure 1.25: Layout of the Forward Spectrometer [58].

# 1.4.2.1 Tracking

In the FS the tracking system is based only on the STT. As shown in Figure 1.26 there are three regions and each one is composed by two detectors. The STTs are constituted of four double layers of straw tubes, two of them with vertical wires while in the two remaining ones the wires are skewed by  $\pm 5^{\circ}$ . This gives the necessary information for the reconstruction in the vertical plane. The first block is placed in the muon filter and has 1024 straws, the second one composed of 4736 straws is placed inside the dipole magnet and the third is the biggest one, featuring 13000 straws, placed after the magnet. These straw tubes are filled with a gas mixture 90:10 Ar-CO<sub>2</sub>, while the drift time is in the order of 140ns depending on the magnet's field strength.

Figure 1.26: Layout of the STT in the FS [58].

#### 1.4.2.2 Dipole magnet

Figure 1.27 shows the magnet structure in the FS. It is a dipole magnet with an opening of 1 m high and of 3 m wide, and a maximum rigidity of 2 Tm [58]. To achieve this rigidity, the structure works with a 2.16 kA current that flows into copper coils. It is placed 3.9 m from the interaction point and it extends for 2.5 m in the beam direction.

The drawback of this structure is the orientation of the magnetic field that is perpendicular to the beam direction. At the full beam momentum, of 15 GeV/c, this implies a deviation of the antiprotons from the nominal direction of  $2.2^{\circ}$ . For this reason, as shown in Figure 1.10, it is necessary to add additional dipole magnets before and after the  $\overline{P}ANDA$  detector in order to adjust this deflection.

Figure 1.27: Layout of the dipole magnet [58].

# 1.4.2.3 Particle identification

In the FS two detectors are used for particle identification as shown in Figure 1.28, the ToF and the Ring Imaging Cherenkov (RICH). The first one will be placed 7 m away from the interaction point, it is composed of three walls of plastic scintillator slabs, each plate 140 cm long and 2.5 cm thick. The readout is placed on top and at the bottom of the slabs, the signal is fed to a photomultiplier tube by a light guide. With this set up, it is possible to achieve a time resolution in the order of 50 ps and ensure a good  $\pi/K$  separation up to 2.8 GeV/c and a good K/p separation up to 4.7 GeV/c [61].

Figure 1.28: Layout for the particle identification detectors.

The structure of the RICH is based on the one used at HERMES [62], a dual radiator made of silica aerogel with refraction index of n = 1.0304 and filled with  $C_4F_{10}$  featuring a refraction index of n = 1.00137. This detector allows a good particle identification in the momentum range between 2 and 15 GeV/c, in particular a good  $\pi/K$  and K/p separation. The Cherenkov light is focused on an array of phototubes, placed outside of the detector, with a mirror.

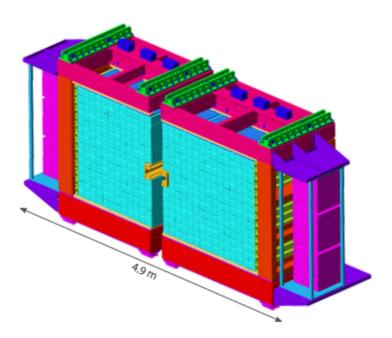

# 1.4.2.4 Shashlyk Calorimeter

The calorimeter designed for the FS is based on the Shashlyk principle. This technique has been chosen for its high performance at a relatively low cost [55, 63] and the resulting layout is shown in Figure 1.29. The light produced is extracted via wavelength shifting fibers placed in the scintillators. The detector will be placed 7.5 m from the interaction point and is realised with 0.275 mm thick plastic scintillators alternated with lead absorber layers with a thickness of 1.5 mm. To achieve a higher spatial resolution, each module is subdivided into four submodules and connected individually to one photomultiplier. The complete structure is made of 351 modules divided into 13 rows and 7 columns. With this structure, an energy resolution of  $4\%/\sqrt{E}$ can be achieved.

Figure 1.29: Layout of the forward calorimeter [63].

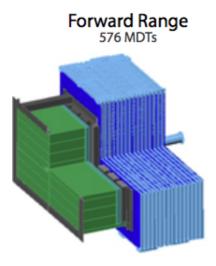

#### 1.4.2.5 Muon detector

The muon detector, shown in Figure 1.30, is placed 9 m from the interaction point. The design is the same as for the muon detector of the TS. However, in this case, it has to manage particles with energies of up to 10 GeV. The MDT aluminium layers are alternated, as in the previous muon detector, with 6 cm thick iron foils. In addition to being able to discriminate between pions and muons, it is possible to use the system as a hadronic calorimeter with moderate energy resolution [64].

Figure 1.30: Layout of the muon detector for the forward spectrometer [63].

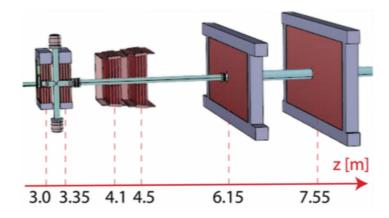

# 1.4.3 Luminosity detector

The general task of the luminosity detector is the determination of the cross section  $\sigma$  of physical processes. The way to obtain this is to extract, in a time interval dt, the time integrated luminosity L and following the relation  $N=L\cdot \sigma$  it is possible to have a correlation between the measured number of events N in a time interval dt and the cross section  $\sigma$  [65]. For  $\overline{P}ANDA$ , this detector will reconstruct the angle of elastically scattered antiprotons in the Coulombnuclear interference region. This angle is particularly small, from 3 mrad to 25 mrad with respect to the beam axis [66]. For this reason, the detector is placed 11 m from the interaction point.

In Figure 1.31 the layout of the detector is shown. It has four tracking planes and each of them is equipped with 10 High-Voltage Monolithic Active-Pixel Sensors (HV-MAPS) modules [68]. In this particular design, 60000 pixels are present in one HV-MAPS with a channel pitch of 80  $\mu m$ . To minimise the scattering of the antiprotons, the detector is surrounded by a box that keeps

Figure 1.31: Layout of the luminosity detector [67].

the vacuum around the detector. To maximise its acceptance, the beam is fed to it through a cone in order to decrease the beam pipe diameter.

# 1.5 Micro Vertex Detector

Since the topic of this thesis is the design of the readout electronic system for the strip sensors of the MVD, this detector is therefore described in more detail on the next pages. As mentioned in Section 1.4.1.1, its main tasks are the reconstruction of decay vertices and the momentum of charged particles. In order to increase the precision as much as possible, the detector is designed to have the hit points as close as possible to the interaction region [45]. Additionally, it must be able to distinguish the primary interaction vertex from the secondary vertices. The distance between the main vertex to the others can vary a lot, in particular, in  $\overline{P}ANDA$ , the decay lengths are roughly from hundreds of microns, i.e.  $c\tau(D^0) = 123 \, \mu m$ , to few centimetres, i.e.  $c\tau(\Lambda) = 7.9 \, cm$  [23].

# 1.5.1 Detector requirements

The design of the detector is mandated by the physics requirements, as well as certain engineering constraints. The volume available for the MVD is limited by the beam pipe and the outer detectors. For the innermost layer, the minimum distance from the center of the beam pipe is 1 cm [69] that is the outer radius of the pipe while, for the outer layer, the maximum

possible distance is 15 cm from the center of the beam pipe in order to not compromise the design of the surrounding detectors. Being the innermost detector leads to another restriction, the material budget. It is important to limit it in order to minimise multiple scattering and consequently reduce the impact on the outer detectors. For the MVD the material budget is limited to 10 % of one radiation length over the full detector acceptance. To maximise the detector acceptance it is necessary that the solid angle is covered fully, but, since there are other detectors surrounding the MVD, the beam pipe positioned in its center and other structures, the polar angle range is limited to 3° to 150°. Besides the mentioned geometrical constraints, the design of a detector largely depends on the physics that is to be investigated. In  $\overline{P}ANDA$ , the nominal interaction rate is  $2 \cdot 10^7 p\overline{p}$  annihilations per second, that means that the MVD will have to deal with high data rates. High data rates, in the order of kHz/channel, heavily affect the granularity of the detector and the development of the sensors and of the readout electronics. In addition, a resolution of around 100  $\mu m$  in z and tens of  $\mu m$  in the x-y plane is necessary to detect secondary vertices. Another consequence of being close to the point of interaction is the high radiation load, it is estimated to be 10 Mrad of total ionising dose and  $10^{13} - 10^{14} n_{1MeVeq} cm^{-2}$  of non-ionising in 10 years of data taking at 50% duty cycle.

# 1.5.2 Detector Layout

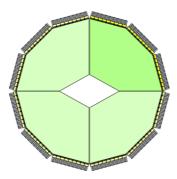

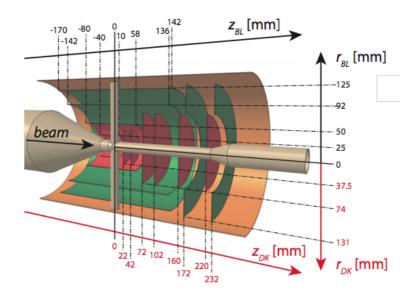

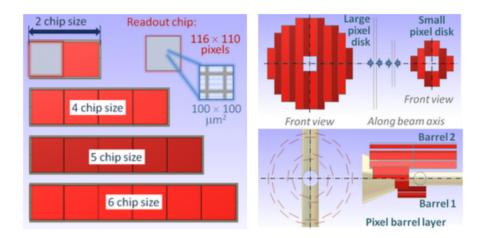

Figure 1.32: Geometrical layout of the MVD [69].

Following the requirements described previously, the basic geometry of the MVD is as follows. It consists of four concentric barrels that surround the beam pipe and six disks in the forward

direction. Since the detector is placed close to the interaction point, a high rate is expected. For this reason, the innermost layers, two barrels and part of the disks, are equipped with hybrid pixel detectors [70]. For the rest of the detector, the two external barrels and the external crowns for the last two disks, double-sided silicon strip detectors are used. The reason for this choice is that the silicon micro-strips are able to cope with the rates predicted in these regions, have a lower material budget than the pixels and are able to readout a large area with less channels [71]. The layout is shown in Figure 1.32. The hybrid pixel layers are given in red, along with the according axes, while the strip layers are given in green (black axes). The zero of the axes is positioned in the interaction point. The inner barrel has a radius of 2.5 cm while the outer layer has a radius of 12.5 cm. For the disks the smaller ones have a radius of 3.75 cm while the larger disks have 7.4 cm as radius for the pixel part and 13.1 cm for the strip crown part.

From Figure 1.32 and Figure 1.33 can be seen that the detector is designed to provide tracking for particles with an angle between  $3^{\circ}$  and  $150^{\circ}$ . With this particular design it is possible to have a minimum of four hit points for tracks between  $9^{\circ}$  and  $140^{\circ}$ . In the *z*-direction the detector extends from -17 cm to 23.2 cm. The operation temperature foreseen for the detector is  $35^{\circ}$ C, therefore a sophisticated cooling system is needed. It is realised using under-pressurised water that is injected with a temperature of  $18^{\circ}$ C.

Figure 1.33: Geometrical layout of the MVD [69].

Every part added increases the material budget of the detector, the major contribution is given by cables for data and voltage supply, amounting to 37.7% of the entire material budget of the detector. The second largest contribution is given by the support structures that result in 28.5%, the cooling pipes account for 13.6%. Only the remaining 20.2% are taken up by the active material itself [45].

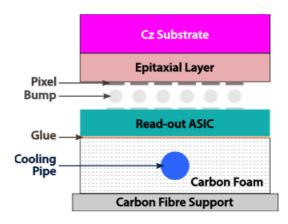

#### 1.5.3 Pixel Detectors

As mentioned in the previous section, there are two different type of sensors, the hybrid pixels and the double sided micro-strips. In the following sensors and their readout are described in more detail.

In the MVD the sensors used to build the inner two barrels and disks are hybrid pixel. This technology is well studied and developed for high energy physics at CERN for the Large Hadron Collider (LHC) experiments. The basic principle is the following: a charged particle crossing the sensor generates electron-hole pairs due to ionisation, and the created pairs are separated by means of applying a reverse bias to the sensor. The charge is then collected and the resulting signal is amplified by the readout electronics that is directly connected to the sensors. Using Czochralski (Cz) wafer as substrate it is possible to grow an epitaxial layer of up to 150  $\mu m$ . The epitaxial layer is segmented on the top creating a diode matrix. The complete structure for the hybrid pixels is then created by soldering each pixel to the corresponding cell on a readout chip through an In or Sn-Pb bump. In Figure 1.34 a cross-section of an hybrid pixel is shown.It is important to remark that the Czochralski substrate is removed at the end of the process in order to minimise the material budget.

Figure 1.34: Cross-section of the hybrid pixel detector[45].

For the MVD each chip features 116 x 110 readout cells, each cell has a square shape of 100  $\mu$ m x 100  $\mu$ m. The pixels are implemented as p<sup>+</sup>-type implants on an n-type epitaxial layer [72]. Since it is necessary to build disks with different radii, it is planned to have four different modules, as shown in Figure 1.35. The total amount of readout channels is  $10.3 \cdot 10^6$ , divided into 338 chips for the barrels and 472 chips in the disks.

Figure 1.35: Pixel modules used to build disks and barrels [45].

As mentioned, each pixel is directly connected to its front-end readout, the Application-Specific Integrated Circuit (ASIC) called Torino Pixel (ToPix), developed in 130 nm CMOS technology [73]. The chip is based on the Time over Threshold (ToT) concept, which means that to measure the charge collected by the sensor, it is sufficient to measure the time that the signal processed by the front-end spends above a fixed threshold. This concept will be explained further in the next chapters.

The ASIC has an input charge range up to 50 fC, a preamplifier noise level lower than 200 e<sup>-</sup> Equivalent Noise Charge (ENC). There are already four different prototypes delivered and tested. The fourth prototype has a power consumption of 120 mW per chip, working at the nominal clock of 160 MHz, leading to less than 800 mW/cm<sup>2</sup>[47]. The time resolution is 6.8 ns with the nominal clock frequency. ToPix serialises the data to send to the off-detector components, it is therefore connected to a Gigabit Transceiver ASIC (GBTX) chip with a bi-directional transmission speed of up to 4.8 GB/s [74].

# 1.5.4 Strip Detectors

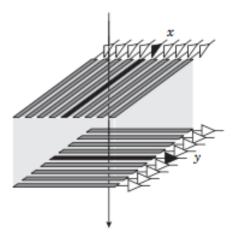

The strips are designed to provide a precise measurement in one direction since the silicon sensor is segmented in narrow strips, while for the second coordinate it is necessary to have a tilted array of strips as shown in Figure 1.36. As for the pixels, each strip is a reverse-biased junction allowing to collect the electron-hole pairs generated in the sensor. The signal is then amplified by the readout electronics positioned on the sensor edge. The achievable resolution with this system is given by the strip pitch p. If the particle hitting the sensor produces a signal on only one strip and assuming a uniform distribution of particles over the strip width,

Figure 1.36: General concept for strip detectors.

the resolution becomes  $\sigma = p/\sqrt{12}$ . It is also possible to increase the spatial resolution if the charge is shared among neighbouring strips [70, 75]. The main advantage with respect to the pixels is that the number of readout channels is lower because one strip can cover a bigger region. The main disadvantage is that the particle rate is lower due to the ghost hit effect. This particular effect happens when two particles, at the same time, hit the strips as shown in Figure 1.37. Two sets of x and y coordinates are registered, and it is not possible to distinguish which is the real hit and which one is the ghost.

Figure 1.37: The two full dots are the real hits, the other two are the ghost points.

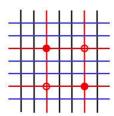

In the MVD, the sensors are double-sided micro-strips. The advantage of this kind of strips is that only one bulk is needed, minimising the material budget. The drawback is that there are some technical difficulties, for example, the proper biasing of the two types. The voltage between the two sides is strongly different, so it is important to isolate the two sides carefully. As in the case of pixels more shapes are needed to build the detector. In particular, rectangular and square shapes are needed for the two external barrels while a trapezoidal shape is needed for the crown of the last two disks. Figure 1.38 shows the layout for the three different modules. There are a few important difference between the barrel sensors and the trapezoidal sensors. The first one is the stereo angle of the strips that is 90° in the square and rectangular sensors

Figure 1.38: Layout of the three different shapes of strip sensors [69].

while for the trapezoidal sensors it is  $15^{\circ}$ . The second important difference is the strip pitch that is  $65 \, \mu m$  in the barrels and  $45 \, \mu m$  in the disks. However, all sensors have the same thickness of  $285 \, \mu m$  and it is expected to put one passive intermediate floating strip between the strips connecting the readout electronics. In this way it will be possible to improve the spatial resolution due to charge sharing [76]. The main properties for the strips are summarised in Table 1.1.

| Parameter     | Value                | Note                                |  |

|---------------|----------------------|-------------------------------------|--|

|               | <10 pF               | Rectangular short strips            |  |

| Capacitances  | <50 pF               | Rectangular long strips             |  |

|               | <20 pF               | Trapezoidal strips                  |  |

| Input ENC     | <800 e <sup>-</sup>  | $C_{sensor} = 10 \text{ pF}$        |  |

|               | <1000 e <sup>-</sup> | $C_{sensor} = 25 \text{ pF}$        |  |

| Dynamic range | 240 ke <sup>-</sup>  | meaning around 38.5 fC (MIP = 4 fC) |  |

Table 1.1: Double sided micro-strip properties [45].

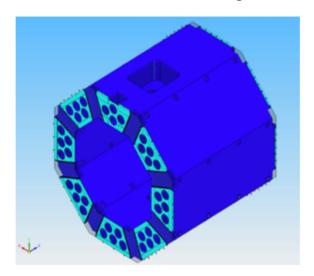

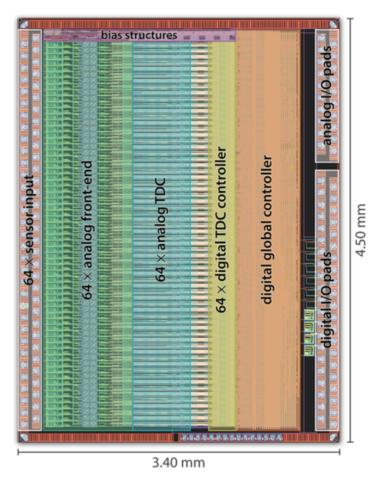

The readout for the strip sensor is called PANDA STrip ASIC (PASTA), it is a highly-integrated front-end. It is produced with a commercial 110 nm CMOS technology, each ASIC has 64 readout channels. Since the design of PASTA is the main topic of this thesis, the details of the design and the characterisation of the prototype are described in detail in the next chapters. To cover the strip part of the MVD, up to 3112 PASTA chips are needed, leading to about 200000

readout channels. The total amount of channels is then 50 times smaller than one for the pixel part while covering more than four times the area.

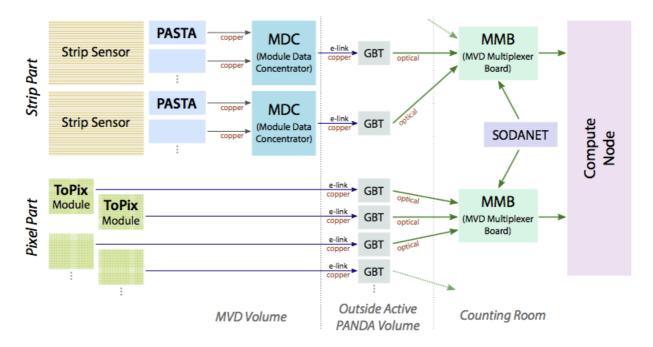

Figure 1.39: Block diagram for the MVD readout system from the sensor to the compute node.

The complete readout system designed for the MVD is shown in Figure 1.39. The strip sensors are readout by PASTA, the information is then processed inside the chip and sent to the Module Data Concentrator (MDC) [77] which is connected to the GBTX. The GBTXs, like in the pixel part, are connected via optical fibre to the MVD Multiplexer Board (MMB) from where the data are sent to the compute nodes.

# PASTA ARCHITECTURE

In the previous chapter, it is described how the MVD is built. It is also shown which are the types of sensors that will be used and the respective readout chips. From this chapter to the last one the focus is on the development and the first tests of PASTA. The ASIC will be described from the top level to the deep structures with a particular focus on the analog Time to Digital Converter (TDC).

# 2.1 Motivation

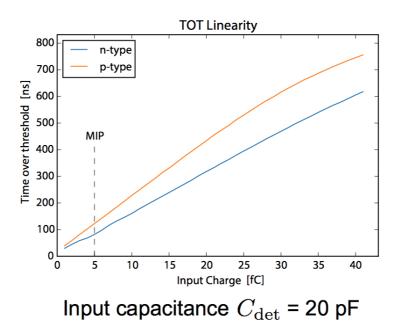

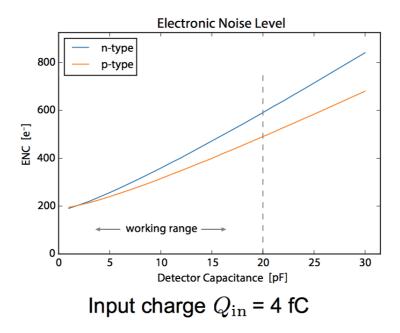

For this project one of the most important requests is directly given by the  $\overline{P}ANDA$  experiment, a trigger-less readout architecture. Another important point is the estimation of the  $\overline{P}ANDA$ 's reaction rate that is up to 20 million collisions per second [2]. From physics simulations, a resolution better than 20 ns is needed to distinguish two different events, thus the readout must be able to determine events, at least, with this time resolution. The average frequency expected of event in a single strip is 40kHz/channel [45]. The last constraint is given by the sensor. As mentioned in 1.5.4, there are three different shapes of strip sensors and this leads to a different input capacitance for the front-end architecture, as shown in Table 1.1.

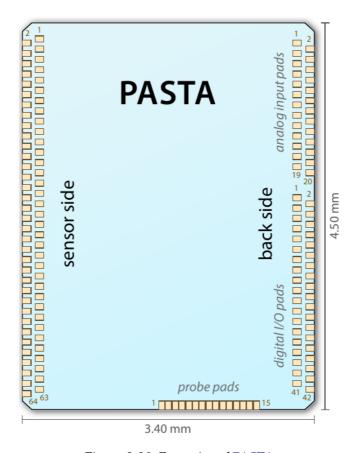

The three different conditions outline a specific profile for the readout. Neither commercial circuits nor ASIC designed for different experiments match with the  $\overline{P}ANDA$  requirements. Nevertheless, to design a custom chip, additional information like size, power consumption and input charge range have to be set according to the MVD requirements and constraints. The main properties of PASTA are summarised in Table 2.1.

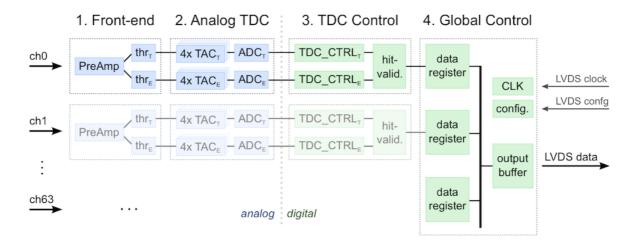

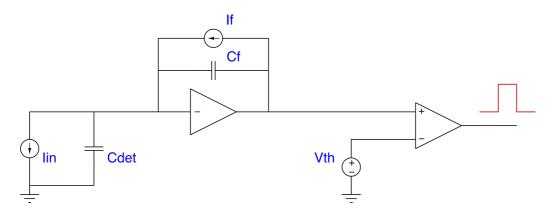

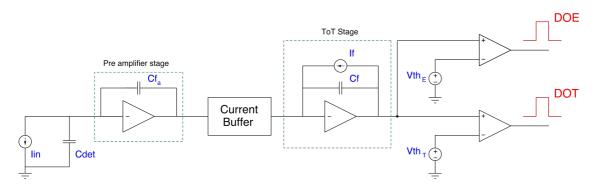

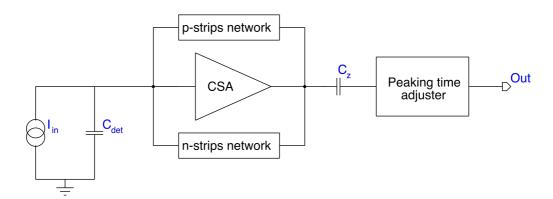

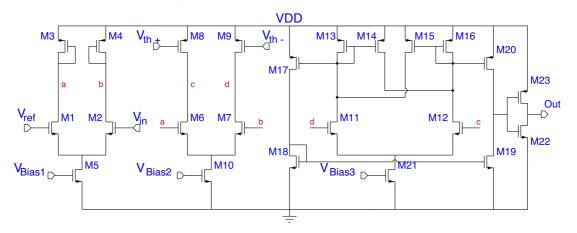

The task of the PASTA chip is to read and pre-processed the signal coming from the strip sensors in order to measure the energy loss of the particles in the silicon sensor. It is built with two different kinds of techniques, the full custom design for the analog part and standard-cell modules for the digital part. The analog part consist of a Front End chain, designed to perform Time over Threshold (ToT) measurements, an analog TDC, necessary to increase the

| Features              |                                                |  |  |  |

|-----------------------|------------------------------------------------|--|--|--|

| Process technology    | 110 nm CMOS                                    |  |  |  |

| Input clock frequency | 160 MHz                                        |  |  |  |

| Input capacitance     | 10 <i>pF</i> to 35 <i>pF</i>                   |  |  |  |

| Input charge          | 1 <i>fC</i> to 38 <i>fC</i> (MIP=4 <i>fC</i> ) |  |  |  |

| Number of channels    | 64                                             |  |  |  |

| Outer dimensions      | $(3.4 \times 4.5) \ mm^2$                      |  |  |  |

| Input pitch           | 63 μm                                          |  |  |  |

|                       |                                                |  |  |  |

| Power consumption     | $\leq 4  mW$ /channel                          |  |  |  |

| Front End noise       | < 600 e <sup>-</sup>                           |  |  |  |

| Maximum capability    | 100 kHz/channel                                |  |  |  |

| Time binning          | 50 ps to 400 ps                                |  |  |  |

| Charge resolution     | 8bit (dyn. range)                              |  |  |  |

| Radiation tolerance   | up to 100 <i>kGy</i>                           |  |  |  |

Table 2.1: Main properties of PASTA [78].

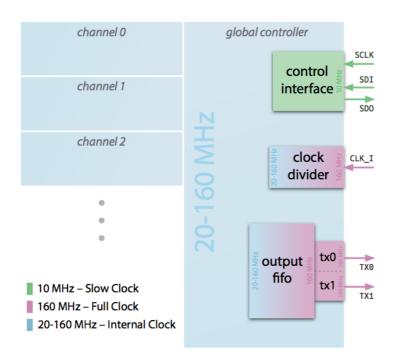

energy resolution and to have a precise time stamp, some drivers and all the bias structures needed for the different architectures. The digital part can be divided into two blocks: the local controller and the global controller. The main task of the first is the configuration of local biasing and the control of all information coming from and to the analog part. It is also connected with the global controller that manages all the information coming from the 64 local controllers. The global controller is also connected to the global bias in order to configure them properly. It assembles all the data and it is the interface between the chip and the external environment through the drivers.

# 2.2 Measurement concept

As already mentioned, the main task of the MVD is to reconstruct the primary and secondary vertex and to contribute to determine the momentum of charged particles. It is important to have a precise time resolution and a very accurate knowledge of the charge deposited in the sensors, without forgetting the constraints, i.e. maximum size of the chip and acceptable power consumption. Similar requests were at the base of the EndoTOFPET-US project, where the Time of Flight for Positron Electron Tomography (TOFPET) ASIC was developed for the readout system of a multi-pixel photon counters [79]. However, some features do not match the  $\overline{P}ANDA$  project as the input capacitance, the input charge, and the absence of radiation hardness protection circuits. The concepts on which the chip is based in interesting anyways.

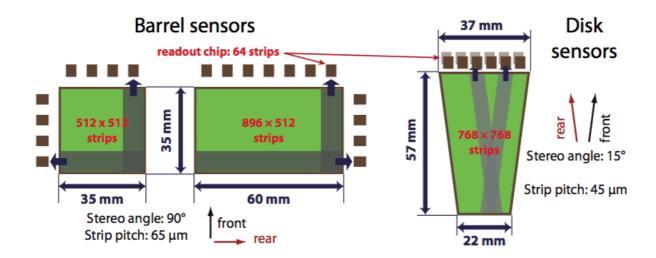

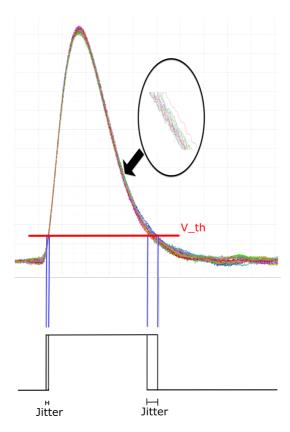

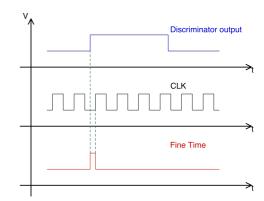

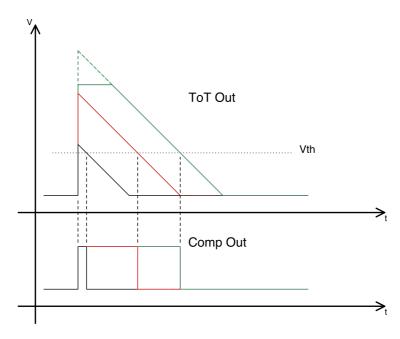

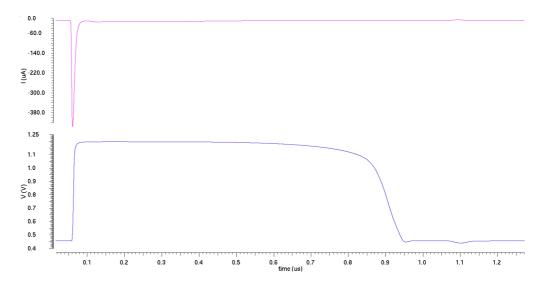

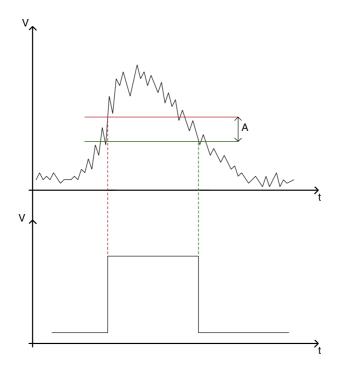

Figure 2.1: Different thresholds problems. In one case the jitter on the trailing edge is much bigger than the second case where the threshold is higher but the time stamp is less precise.

The basic idea is to obtain the charge information and the time stamp through a ToT measurement. The ToT technique is very powerful because it guarantee the linearity even if the signal

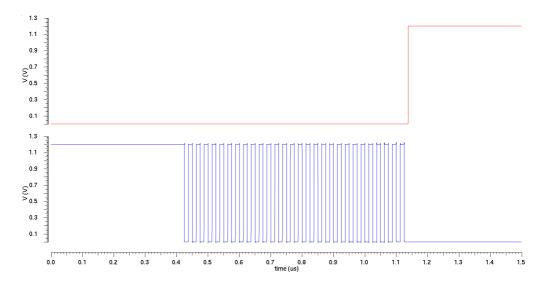

is saturated. It permits to handle a large charge range of input signals. In fact the technique works in such way that the charge information is obtained measuring the distance between the leading edge and the trailing edge of the signal forgetting its amplitude, leading to a specific Front End design. At the end of the amplification chain, when the signal has been amplified enough, there is a discriminator which distinguish the signals from the noise. The threshold value is an important parameter for the discriminators. If the threshold value is close to the baseline it is possible to achieve a precise time stamp for the leading edge but it is much more sensitive to noise fluctuations. The noise fluctuation are even more relevant, as it is possible to see in Figure 2.1, on the trailing edge, since its slope  $\frac{\Delta V}{\Delta t}$  decrease with the approach of the baseline. On the other hand, if the threshold value is set higher it is possible to significantly reduce the effect of the noise fluctuations in the trailing edge but the precision for the time stamp in the leading edge is decreased.

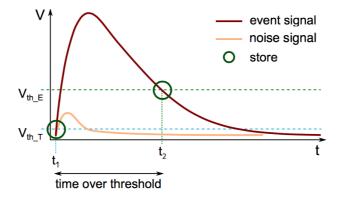

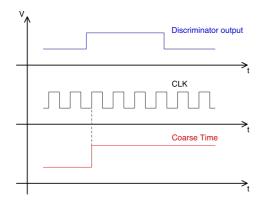

To solve this problem it has been decided to use two different discriminators with two thresholds. The discriminator featuring the lower threshold is called *Time Discriminator* while the one with the higher threshold is called *Energy Discriminator*. Each discriminators produce a signal which suffer of large jitter, in the falling edge in the first case and in the rising edge in the second case. In order to solve these problems in PASTA, to perform ToT measurements, the rising edge of the first discriminator and the falling edge of the second discriminator are used as shown in Figure 2.2. In this way it is possible to reach a good time resolutions from both edges. Moreover, using this technique it is possible to decrease the sensibility to the noise, in fact the event to be stored must crosses both the thresholds.

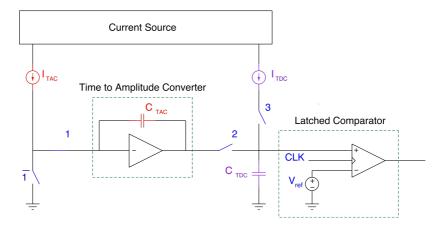

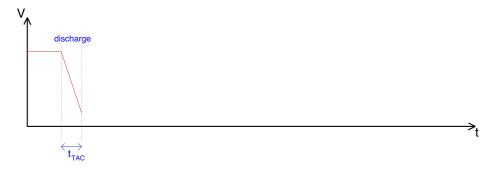

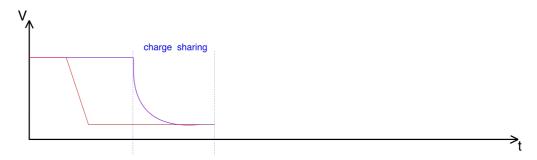

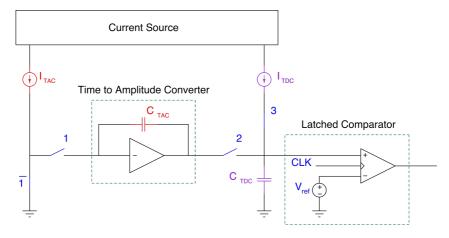

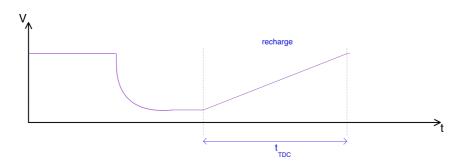

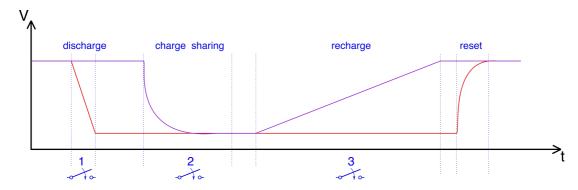

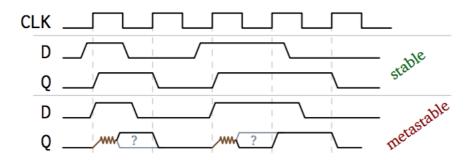

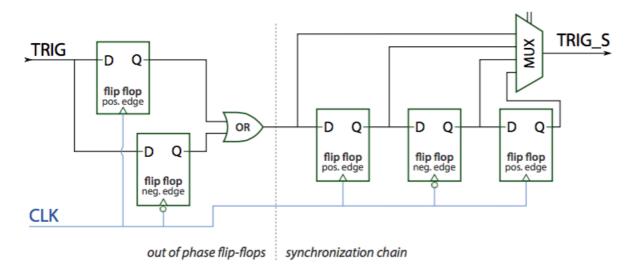

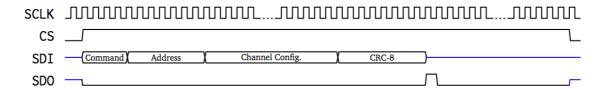

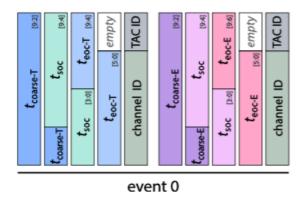

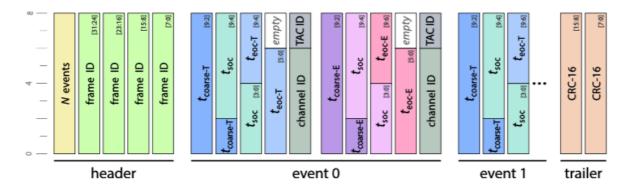

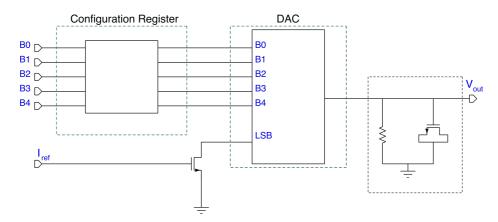

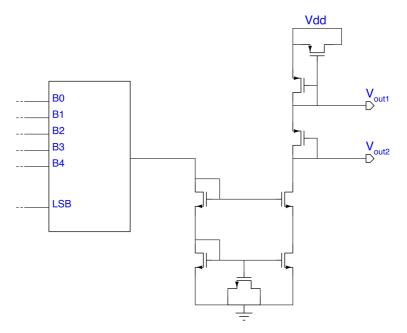

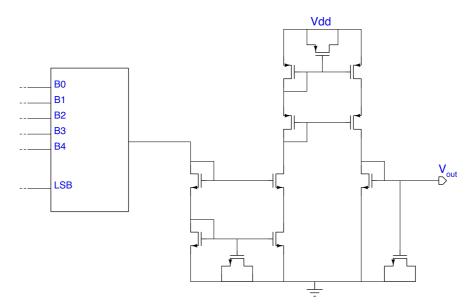

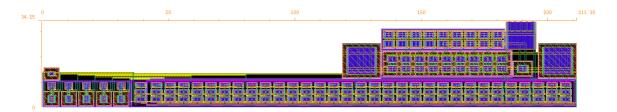

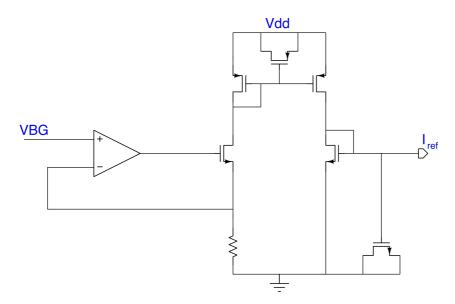

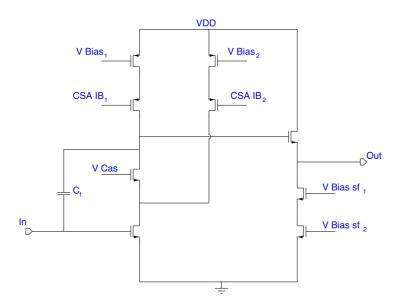

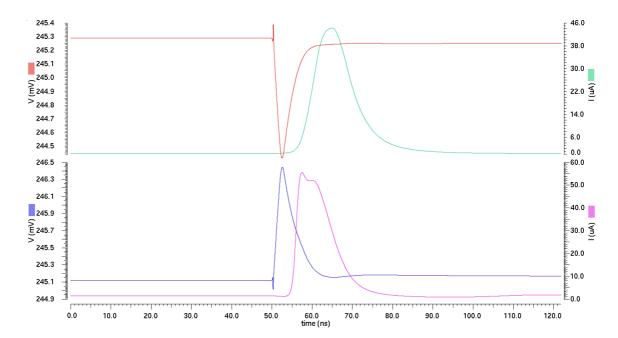

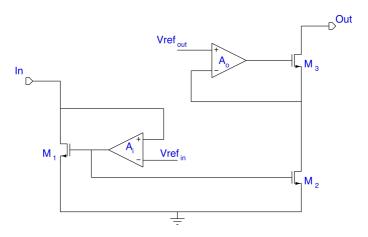

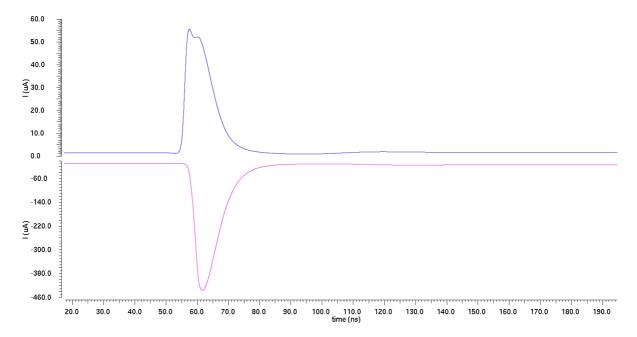

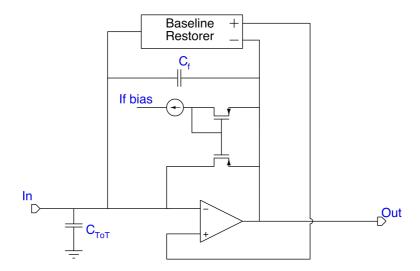

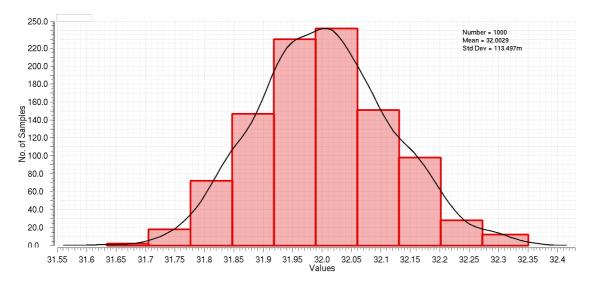

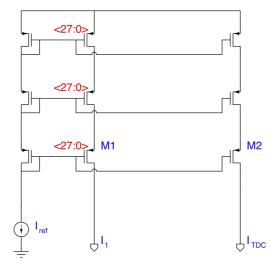

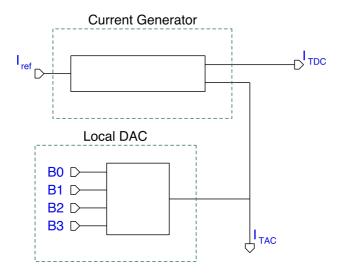

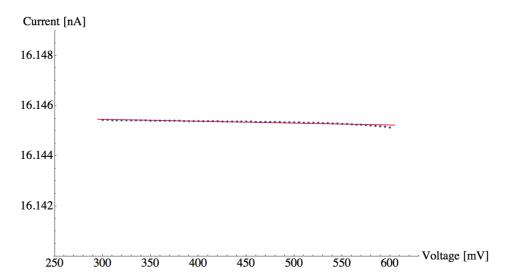

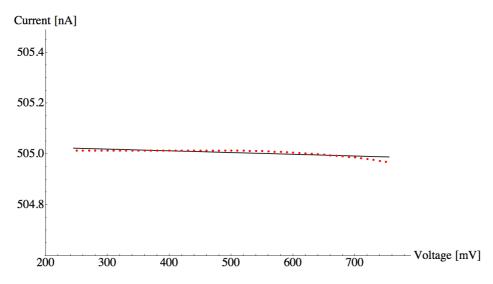

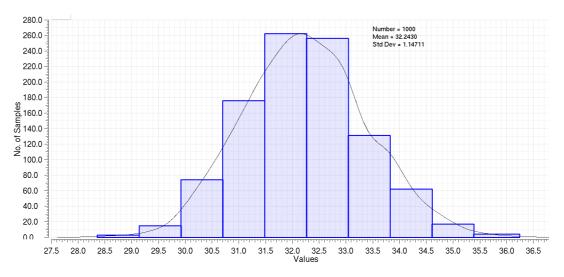

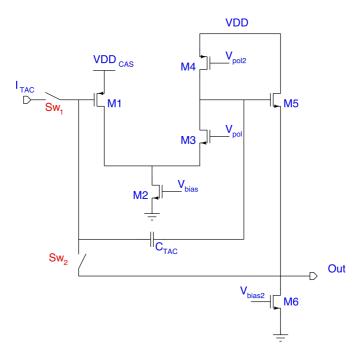

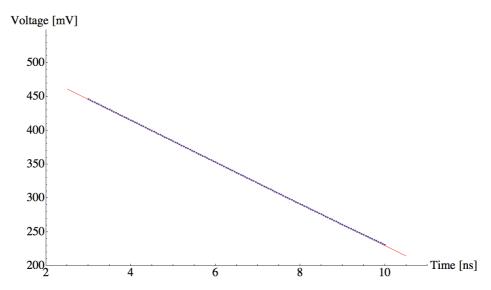

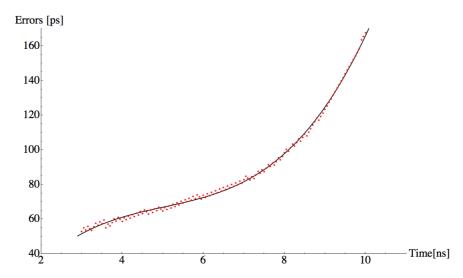

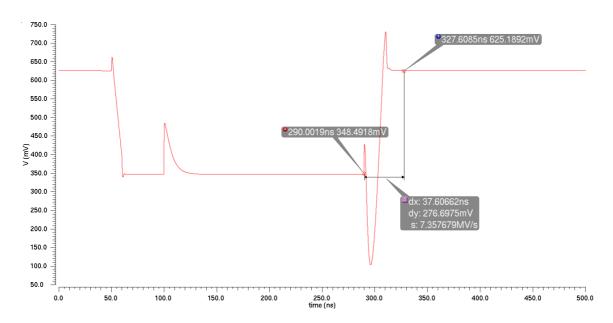

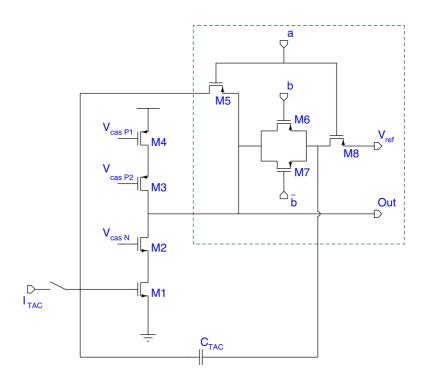

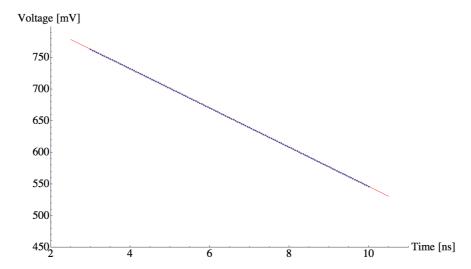

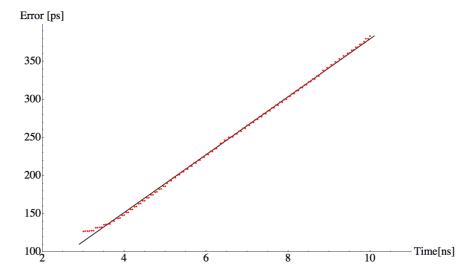

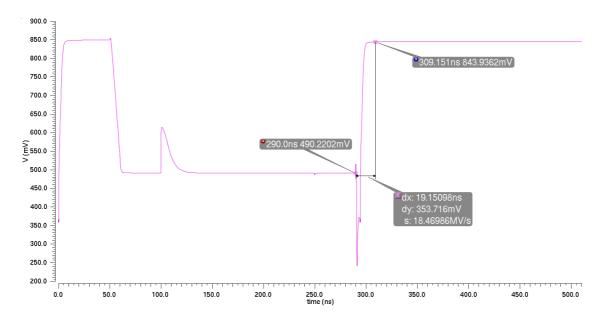

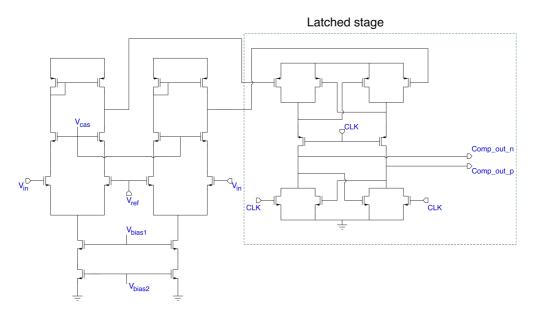

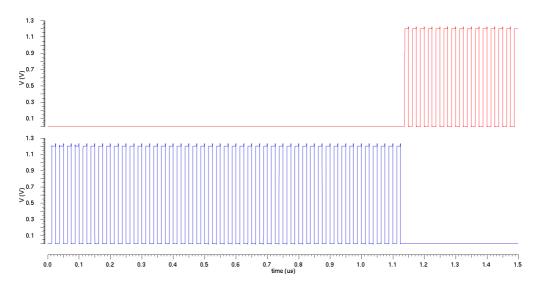

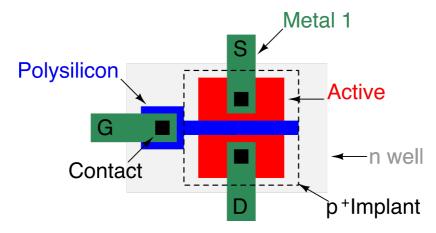

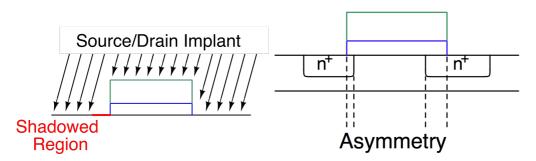

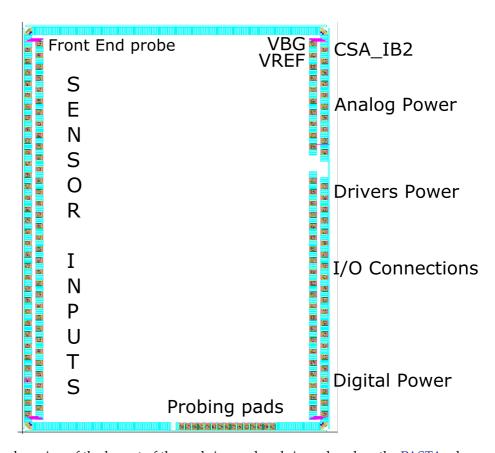

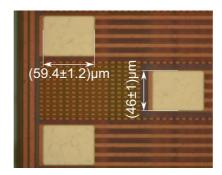

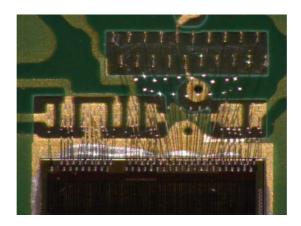

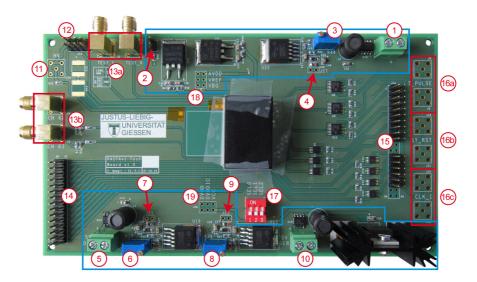

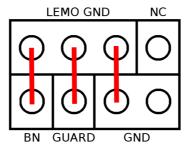

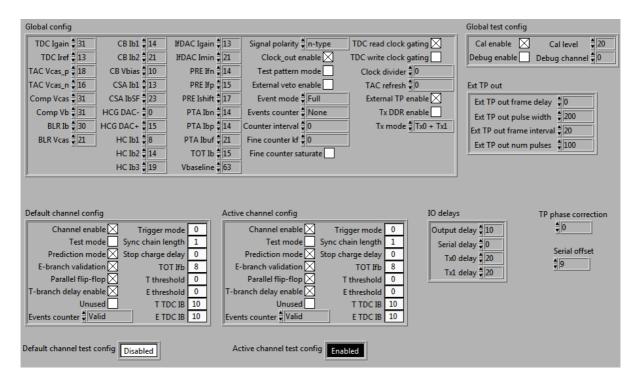

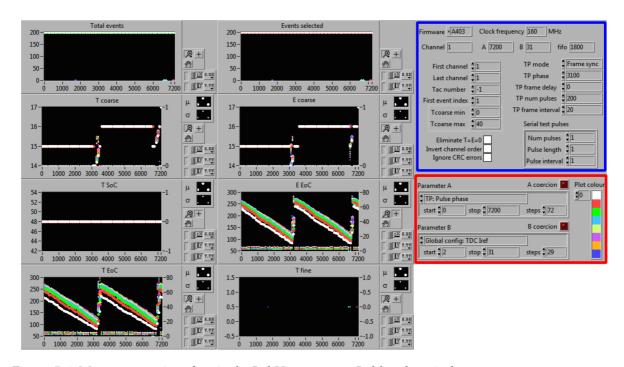

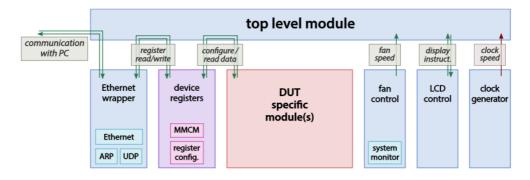

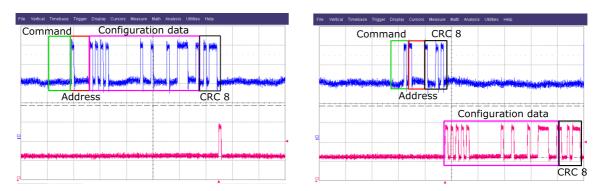

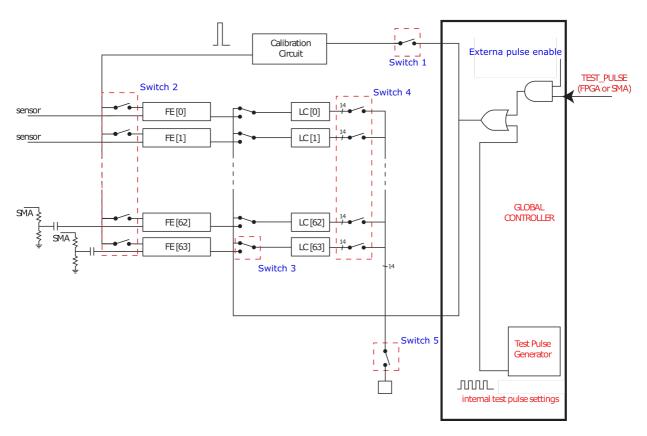

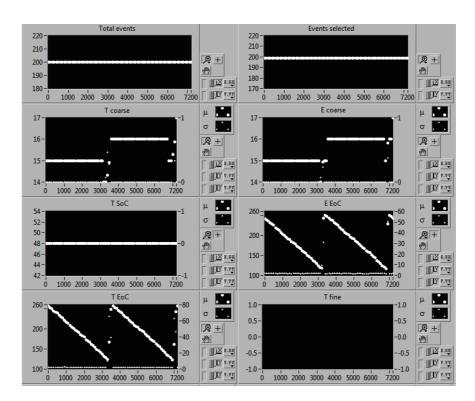

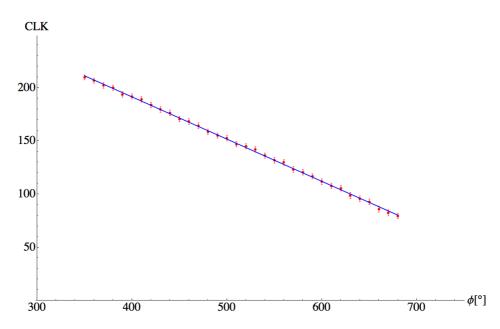

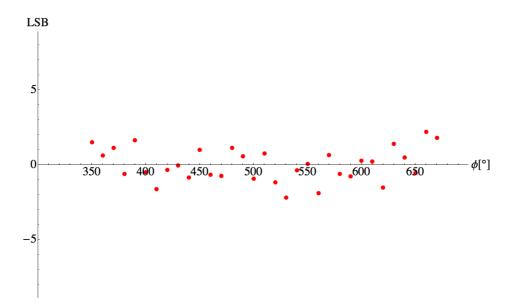

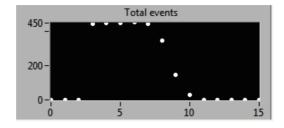

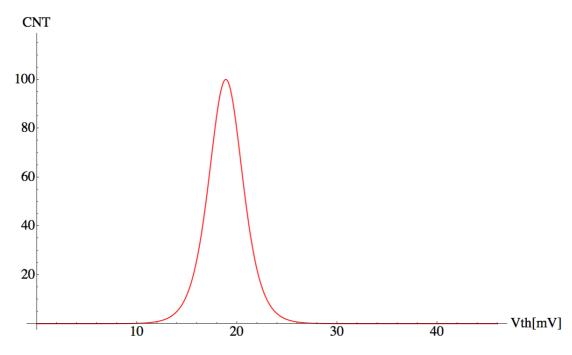

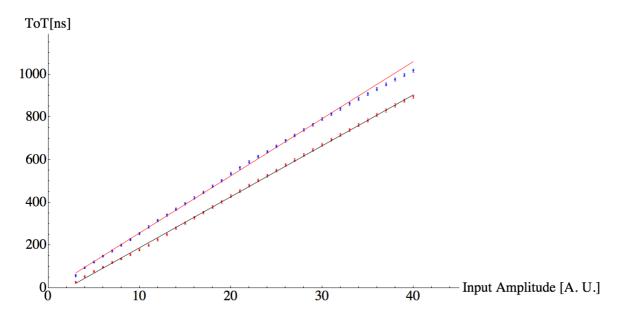

# Measurement Concept Inspired by TOFPET