## The role of a diffusion barrier in plasma display panel with the high gamma cathode layer

Tae-Ho Lee, <sup>1</sup> Hee-Woon Cheong, <sup>1</sup> Ohyung Kwon, <sup>1</sup> Ki-Woong Whang, <sup>1,a)</sup> Sven Ole Steinmüller, <sup>2</sup> and Jürgen Janek <sup>2</sup>

(Received 30 June 2011; accepted 27 September 2011; published online 24 October 2011)

Plasma display panel (PDP) with MgO-SrO double cathode layer and  $SiO_2$  diffusion barrier is proposed to make the SrO layer free of contaminations. Time of flight-secondary ion mass spectrometry (TOF-SIMS) analysis shows the diffusion of impurities, like Na and K, can be effectively blocked while a new SrO layer is formed on top of the MgO layer. This structure shows that high Xe gases can be used to improve the luminous efficacy 2.3 times and decrease the voltage margin more than 10 V compared to the conventional PDP using Ne-Xe 15%. The aging time was also significantly decreased to 3-4 h. © 2011 American Institute of Physics. [doi:10.1063/1.3655329]

Plasma display panel (PDP) can provide vivid, high quality images and so is suited for the display of realistic 3dimensional (3D) images. PDP has made big improvements in its luminous efficacy and power consumption over the years, but still needs further progress in order to meet the green products requirements. One of the effective methods used to reduce the discharge voltage and increase the luminous efficacy of a PDP is to use a high gamma cathode layer. MgO has been one of the most widely used cathode materials; however, it has limitations because of the large band gap energy of about 7 eV, too large to induce the secondary electron emissions through the Auger neutralization process using Xe ions.<sup>2–4</sup> There have been many attempts to apply other alkaline earth metal oxides such as SrO and CaO, which have a lower band gap energy and, therefore, a higher secondary electron emission coefficient for Xe ions when compared to MgO.<sup>5,6</sup> However, these materials have limitations when applied to PDP using the normal fabrication process, since they are very unstable and highly reactive with H<sub>2</sub>O or CO<sub>2</sub>, resulting in the formation of hydroxides or carbonates when exposed to air. In a recent research, which used a mixture of SrO and CaO, the luminous efficacy almost doubledwith a Ne-Xe 30% content gas compared to that of a panel using the conventional MgO employing Ne-Xe 10%. However, the panel assembly fabrication process needed to be carried out in either a nitrogen gas atmosphere or in a vacuum. Another method which does not require a special sealing process but still allows the use of the high gamma property of SrO or CaO had been suggested. It uses a double cathode layer structure consisting of a maincathode layer of an alkaline earth metal oxide like SrO and a protecting MgO layer. It has been shown that a panel with the double cathode layer could retain the high gamma properties of the SrO main-cathode layer, so that the high luminous efficacy and low driving voltage could be realized even

though the conventional sealing process was used. However, the panels with the double cathode layer or binary alloy needed a long aging time of 30–40 h for the stabilization of the discharge voltages, compared to the MgO single cathode layer panel. Based on the findings from the time of flight-secondary ion mass spectrometry(TOF-SIMS) analysis of the cathode layer, we suggest a diffusion barrier between the dielectric and cathode layers in order to prevent the contamination of the cathode layer by impurities originating from the underlying dielectric layer, electrode, and glass substrate, which occurs during the high temperature sealing process.

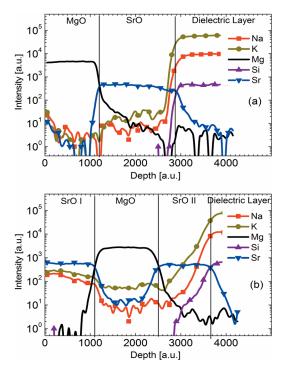

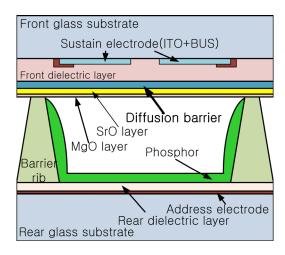

The cathode layer is deposited after forming a transparent dielectric layer on front glass substrate. The substrate is then aligned and sealed with a rear glass substrate and sintered at a peak temperature of 450 °C for 4 h. Finally, the assembled panel undergoes a thermal annealing process at a temperature of 360 °C for 6 h in order to outgas and exhaust all of the residual gases. During the sealing and annealing processes, some elements like sodium and potassium come out from the dielectric layer, electrode, and glass substrate and diffuse into the cathode layer, as shown in Fig. 1, which shows the vertical distribution of the elements in the cathode and dielectric layers obtained by TOF-SIMS (TOF-SIMS V, Ion-ToF GmbH). Fig. 1(a) shows the as-deposited layers and (b) the layers after experiencing the high temperature sealing process. Fig. 1(a) shows a clear layer structure for the MgO, SrO, and dielectric layers, whereas an outward diffusion of Sr through the MgO layer forms a new SrO I layer on top of the MgO and at the same time, the diffusion of Na, K through the SrO and MgO layers accumulates on the surface of the newly formed SrO I layer. In order to reduce the contamination of SrO, a 1 µm thick SiO<sub>2</sub> layer is inserted as shown in Fig. 2. The plasma-enhanced chemical vapor deposition (PECVD, 310PC, Surface Technology System) method is used in order to deposit SiO<sub>2</sub> at 200 °C with 5%  $SiH_4/N_2$  (160 sccm),  $N_2O$  (1500 sccm), and  $N_2$  (240 sccm) gases at 73.3 Pa. The deposition rate was 34 nm/min when

$<sup>^{1}</sup>$ Plasma Laboratory, Department of  $\bar{E}$ lectrical Engineering and Computer Science, Seoul National University, 599 Gwanak-ro, Gwanak-gu, Seoul 151-742, Korea

<sup>&</sup>lt;sup>2</sup>Physikalisch-ChemischesInstitut, Justus-Liebig-University Giessen, Heinrich-Buff-Ring 58, D-35392 Giessen, Germany

a)Author to whom correspondence should be addressed. Electronic mail: kwhang@snu.ac.kr.

FIG. 1. (Color online) The element distribution obtained by the TOF-SIMS. (a) As-deposited SrO-MgO double cathode layer. (b) The same sample after furnace process at  $450\,^{\circ}\text{C}$  for  $4\,\text{h}$ .

60 W of RF power was applied. In order to verify the effect of the diffusion barrier, 2 in. test panels with 50 in. full high definition (FHD) resolution specifications were fabricated and tested for the experiment as shown in Table I.

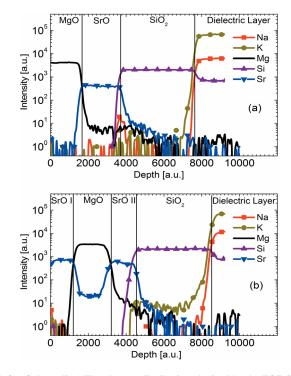

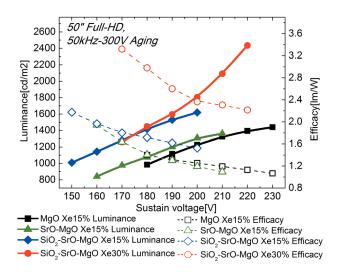

Fig. 3 shows the vertical distribution of elements in the cathode and dielectric layers of the panels with the  $1 \mu m$  thick SiO<sub>2</sub> layer before (Fig. 3(a)) and after (Fig. 3(b)) the 4 h 450 °C high temperature process. Fig. 3(a) shows the clear layer structure of the SrO-MgO double cathode with the SiO<sub>2</sub> diffusion barrier between the SrO and dielectric layers. In Fig. 3(b), we can find the Sr diffusion through the MgO layer and formation of a new SrO I layer on top of the MgO. The diffusion of the Na and K through SiO<sub>2</sub> is blocked effectively, so that their levels inside of the newly formed SrO I layer are negligible. Fig. 4 shows the luminance and

FIG. 2. (Color online) The schematics of suggested double cathode layer with the diffusion barrier.

TABLE I. The test panel specifications.

| Parameter                 | Value                         |

|---------------------------|-------------------------------|

| Resolution and cell pitch | 50 in. FHD and 576 μm         |

| Front dielectric          | $\epsilon$ =12 and 30 $\mu$ m |

| Barrier rib height        | $120  \mu \mathrm{m}$         |

| ITO gap                   | $60  \mu \mathrm{m}$          |

| MgO layer thickness       | 500 nm                        |

| SrO-MgO layer thickness   | SrO: 500 nm, MgO: 120 nm      |

| Phosphor                  | Monochrome green              |

| Aging conditions          | Square pluses/50 kHz, 300 V   |

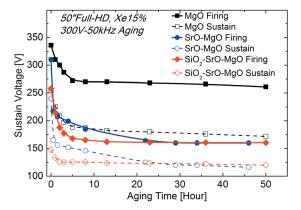

luminous efficacy of the panels with the different types of cathode layers. The reference values are taken from the panel with the single MgO layer and the Ne-Xe 15% gas. When a SrO-MgO double cathode layer is used, the panel with the Ne-Xe 15% shows a 20 V reduction in the lower end of the voltage margin and 40% increase in the luminous efficacy. However, it took 30–40 h of aging for this double cathode layer panel to have stabile voltages, as can be seen in Fig. 5, which shows the variation of the firing and sustain voltages according to the aging time for the various types of cathode layers.

When the SiO<sub>2</sub> diffusion barrier is adopted, the panel using Ne-Xe 15% gas shows a 30 V reduction in the lower end voltage margin and a 55% increase in the luminous efficacy compared to the reference panel. In addition to these improvements in the voltage margin and luminous efficacy, a more important improvement occurs regarding the aging time, as can be seen in Fig. 5, when the SiO<sub>2</sub> diffusion barrier is adopted. It can be seen that the long 30–40 aging time needed for the panel with the SrO-MgO double cathode layer without the diffusion barrier is now reduced to 3–4 h when

FIG. 3. (Color online) The element distribution obtained by the TOF-SIMS. (a) As-deposited SrO-MgO double cathode layer with the  $SiO_2$  diffusion barrier. (b) The same sample after furnace process at 450 °C for 4 h.

FIG. 4. (Color online) The luminance and luminous efficacy of the various panels.

the SiO<sub>2</sub> diffusion barrier is adopted. Fig. 4 also shows that even when the Xe content is increased to 30%, if the panel has the SrO-MgO double cathode layer with the diffusion barrier, its lower voltage margin is still smaller by 10 V but the highest measured luminous efficacy is 2.3 times larger when compared to the reference. Considering that the Xe content in the reference panel is 15%, this low voltage characteristic of panel with 30% Xe gas markedly shows the benefit of using high a gamma cathode material like SrO. A life time test shows that the PDP with the SrO-MgO double cathode layer exhibits a longer life time than that of one with the traditional MgO single cathode layer which can be ascribed to the low voltage characteristic of the former one.

In conclusion, the importance of the prevention of contamination in the cathode layer is reported in PDP. Through the analysis of cathode layer using a TOF-SIMS, it has been found that impurities like Na and K in the dielectric layer, electrode, and glass substrate diffuse through the cathode layer during the high temperature sealing process and accumulate on the cathode surface, which eventually leads to the increased driving voltage and aging time and decrease in luminous efficacy. This diffusion can be effectively blocked by the adoption of a SiO<sub>2</sub> diffusion barrier made using the PECVD method. When the panel adopted this diffusion

FIG. 5. (Color online) The driving voltage variations according to the aging time with the MgO single layer, the SrO-MgO double layer, and the SrO-MgO double layer with the SiO<sub>2</sub> diffusion barrier.

barrier togetherwith the SrO-MgO double cathode layer, it showed one order of magnitude decrease in the aging time and a greatly improved luminous efficacy at reduced voltages when compared to those of the panel equipped with the conventional MgO cathode layer without the diffusion barrier.

<sup>1</sup>ENERGY STAR<sup>®</sup> Program Requirements Product Specification for Televisions, Eligibility CriteriaVersion 5.3, U.S. Environmental Protection Agency.

<sup>2</sup>G. Oversluizen, T. Dekker, M. F. Gillies, and S. T. de Zwart, J. Soc. Inf. Disp. 12, 51 (2004).

<sup>3</sup>G. Oversluizen, S. de Zwart, T. Dekker, and M. F. Gillies, in *Digest of Technical Papers of 2002 Society for Information Display International Symposium* (Society for Information Display, Boston, 2002), p. 848.

<sup>4</sup>Y. Motoyama, Y. Murakami, M. Seki, T. Kurauchi, and N. Kikuchi, IEEE Trans. Plasma Sci. **54**, 1308 (2007).

<sup>5</sup>T. Shinoda, H. Uchiike, and S. Andoh, IEEE Trans. Electron Devices **26**, 1163 (1979).

<sup>6</sup>H. Uchiike, K. Sekiya, T. Hashimoto, T. Shinoda, and Y. Fukushima, IEEE Trans. Electron Devices **30**, 1735 (1983).

<sup>7</sup>K. Whang, H. Jung, T. Lee, and H. Cheong, in *Proceeding of the 10th International Meeting on Information Display* (Korean Information Display Society, Ilsan, Korea, 2009), p. 173.

<sup>8</sup>Y. Motoyama, D. Kato, and M. Seki, in *Proceedings of the 17th International Display Workshop* (Society for Information Display, Fukuoka, Japan, 2010), p. 959.

<sup>9</sup>H. Jung, T. Lee, O. Kwon, H. Cheong, S. Steinmüller, J. Janek, and K. Whang, IEEE Electron Device Lett. **31**, 686 (2010).

<sup>10</sup>K. Kim, J. Kim, J. Tang, K. Whang, and S. Lee, J. Kor. Vac. Soc. 8, 482 (1999).